No: 1

Date: 17/2/78

#### Information on 2900 Image Store

(Received verbally by J.K. Yarwood from Alan Darling and Bill Kell, 4th May, 1977; updated June 1977; updated with the help of Pat Ryan January 1978.)

The purpose of the discussion was to establish differences between the 2980 and the 2976, 2970 & 2960 with a view to trying EMAS 2900 on the former. The following table summarises the model-dependent addresses and uses for the four machines:

|                                         | 2960.Bits           | SML16 2970.Bits  | 2976.Bits        | SML12 2980.Bits         |

|-----------------------------------------|---------------------|------------------|------------------|-------------------------|

| OCP Registers                           |                     |                  |                  |                         |

| LST Base                                | 00006001            | 00006001         | 402A             | 402A                    |

| LST Limit                               | 6000                | 6000             | 402C             | 402C                    |

| PST Base                                | 6003                | 6003             | 4029             | 4029                    |

| PST Limit                               | 6002                | 6002             | 402B             | 402B                    |

| Handkeys                                | 6006                | 6006             | 4205             | 4205                    |

| Hooter (set bit to commence hoot;       | 6008 <b>31</b>      | 6008 31          | 4013 19          | 4013 <b>19</b>          |

| clear bit to terminate hoot)            | (Optional)          |                  |                  |                         |

| System Interrupt Register               | 600A 28 <b>-3</b> 1 | 600A 28-31       | 4014 22-27       | 4014 22 <del>-</del> 27 |

| (Bit set to indicate interrupting Port) | for Ports 0 to 3    | for Ports 0 to 3 | for Ports 0 to 5 | for Ports 0 to 5        |

| Real time clock (X)                     | 600C                | 600C             | 44pt 4000        | 44pt4000                |

| Real time clock (Y)                     | 600D                | 600D             | 44pt4100         | 44pt4100                |

| Real time clock (Z)                     | 600E                | 600E             | 44p/t4200        | 44pt4200                |

|                                         |                     |                  | (see footnote)   | (see footnote)          |

|                                                                           | 2960.Bits | SML16 2970.Bits        | 2976.Bits       | SML12 2980.Bits          |

|---------------------------------------------------------------------------|-----------|------------------------|-----------------|--------------------------|

| OCP Control Registers                                                     |           |                        |                 |                          |

| Control (inhibit when set)                                                | 6011      | 6011                   | 4013            | 4013                     |

| Clear slaves - write only (reads 0)                                       | 0         |                        |                 |                          |

| Inhibit CPRs                                                              |           | 24                     |                 |                          |

| Inhibit main store                                                        |           | 25                     |                 |                          |

| Inhibit retry                                                             |           | 26                     | 13              | 13                       |

| Inhibit pipeline                                                          |           | 27                     | 12 (non         | overlap) 12 (non overlap |

| Inhibit stack slave                                                       |           | 28                     | 20              | 20                       |

| Inhibit instruction slave                                                 |           |                        | 23              | 23                       |

| Inhibit operand slave                                                     | 28        |                        | 28              | 28                       |

| Inhibit full photo                                                        | 31        |                        |                 |                          |

| Lock translation slave rejection                                          |           |                        | 25              | 25                       |

| Software Gen. System Error                                                | 6013      | 6013                   | 4013 17         | 4013 17                  |

| Register Load ('Activate')                                                | 6014      | 6014                   | not implemented | not implemented          |

| SMAC Image Store                                                          |           |                        |                 |                          |

| SMAC config. register (one per SMAC)<br>(s = SMAC ident no, in range 0-F) | 4C0s6A20  | 4C0s6A20               | 4Cs04A20        | 4Cs04A20                 |

| Available blocks                                                          | 8-23      | 8-23                   | 8-23            | 7-22                     |

|                                                                           |           | ), bit 22=block 1, bit |                 | bit 7=block 0,           |

|                                                                           |           |                        |                 | bit 8=block 1, etc       |

| SMAC blocksize                                                            | 128K /256 | 128K /256              | 128K            | 256K                     |

NPE 2970-25-000 Sheet: 9.9.1

| I.S.                             | 4CXX6004                                                                    | 4CXX6100                                                    | 4CXX6A00                                                          | 4CXX6A10                                                             | 4CXX6A20                                                                     |

|----------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------|

| Data<br>bit<br>No.               | Failing Data                                                                | Failing Address                                             | Status                                                            | Engineering Status                                                   | Configuration                                                                |

| 32<br>33<br>34<br>35<br>56<br>60 | Hamming Parity 2 2                                                          | Address Parity                                              | · <b>'</b>                                                        | On Margins Inhibit Hamming Check Inhibit Hamm. Report On 'Engineers' | 0 BLK Conf as Ø<br>1 "<br>2 "<br>3 • "                                       |

| 36 29<br>37 23<br>38 g           | Hamming Parity 4-% -                                                        | Address bit 06                                              |                                                                   | Basic Unit Select Add. Unit Select Add. Unit Select Add. Unit Select | DAC<br>16K SMC                                                               |

| 40<br>41<br>42<br>43             |                                                                             | Address bit 10- Address bit 11-                             | Port O Fail Port 1 Fail Port 2 Fail Port 3 Fail                   | some # hus mue                                                       | Block 15 On line Block 14 On Line Block 13 On Line Block 12 On Line          |

| 44<br>45<br>46<br>47             |                                                                             | Address bit 12 Address bit 14 Address bit 15                | Hamm. Gen. Fail<br>Hamm. Corr. Fail<br>I.S. NACK                  |                                                                      | Block 11 On Line<br>Block 10 On Line<br>Block 09 On Line<br>Block 08 On Line |

| 48<br>49<br>50<br>51             | Byte O Parity Fail Byte 1 Parity Fail Byte 2 Parity Fail Byte 3 Parity Fail | Address bit 16 Address bit 18 Address bit 19                | Byte Parity Fail Address Parity Fail Byte Func.Par.Fail           |                                                                      | Block 07 On Line<br>Block 06 On Line<br>Block 05 On Line<br>Block 04 On Line |

| 52<br>53<br>54<br>55             | Byte 4 Parity Fail Byte 5 Parity Fail Byte 6 Parity Fail Byte 7 Parity Fail | Address bit 20 Address bit 21 Address bit 22 Address bit 23 | MBHE The REGUL<br>Multibit Hamm. Fail f                           | of needs                                                             | Block 03 On Line Block 02 On Line Block 01 On Line Block 00 On Line          |

| 56<br>57<br>58<br>59             | `                                                                           | Address bit 24 c                                            | Singlebit Hamm. Fail Reading Fault  PCUS Toggle Set Holding Fault | Marginate + 5v Marginate - 5v Marginate 19v Marginate 3.5v           | Not Matural SMAC No. Be SMAC No. 1 Port O Closed Port 1 Closed               |

| 60<br>61<br>62<br>63             |                                                                             | Address bit 28<br>Address bit 29                            | Control Parity Fail A.U.Addr.Par. Fail                            | +5v Margins High -5v Margins High 19v Margins High 3.5v Margins High | Port 2 Closed Port 3 Closed BLK 1 in BU BLK Ø in BU                          |

#### SAC Trunk Register Image Store (2980 only)

DATA IN (B->A)

SPAD 40pt4000 0-31 contents 4100 32-63 (i.e. RAM) 4200 64-95 4300 96-127

#### SAC Registers

These are all model-independent.

#### [Footnotes:

1) 2980 Real-time Clock

pt is where you get the IPL interrupt from: p is normally 0 and t is "don't care" (zero).

You must also set the appropriate port bit in 4012 (bits 16 to 25 = Ports 0 to 5) to allow SAC external interrupts to reach the OCP.

The Real-time clock on the 2980 is out in a (the) SAC,

The 2976 is as the 2980 but p' = OCP port.

2) 2960 Real Addressing Mode

This is now thought to be available.]

J.K. Yarwood P.D. Stephens

## Image store locations on P2; subblock 60

All locations are read/write unless otherwise specified (or reserved)

```

6000

LSTB0

6001

LSTB1

PSTB0

6002

_

6003

PSTB1

6004 -

Reserved

6005 -

Reserved

6006

Handkeys (read only)

Machine type (read only)

Hooter (read zero, write bit 2**0 to set/clear hoot)

6007

6008

Broadcast system errors (bit 2**0) (read and write)

6009

600A

System interrupt mask

600B

Communications SMAC number

600C

RTCX

600D

RTCY

600E

RTCZ

-

Clock module number

600F

6010

Reserved

CPU mode and control

6011

Reserved

6012

Cause system error (read zero, write to bit 2**7)

6013

Block 0 activate (write only)

6014

Reserved

6015

Upper lights (write only)

6016

- Lower lights (write only)

6017

Stop machine (write only)

6018

```

R.D. Eager 17th August 1982

## Details of image store X6011 on P2

### Image store read

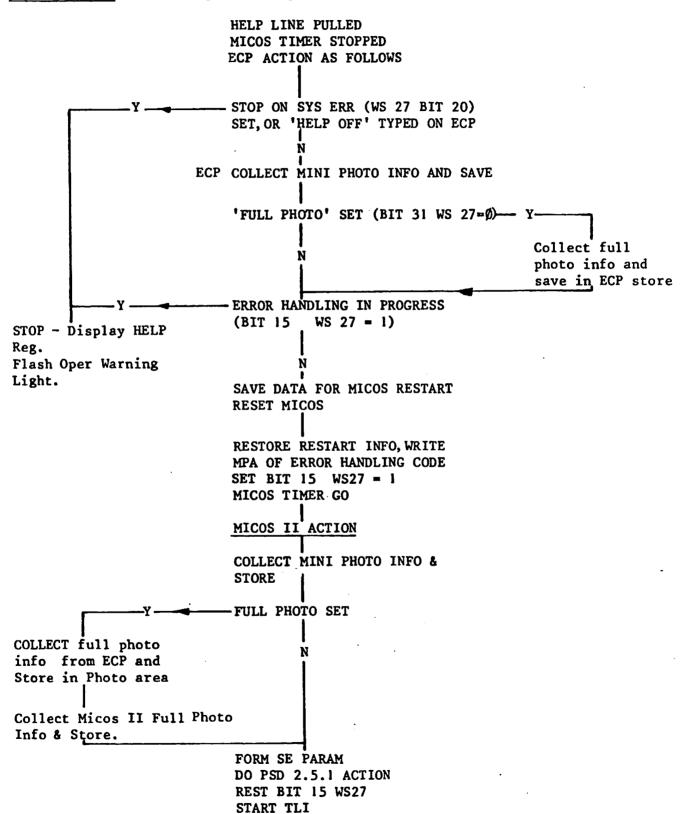

A read returns bits 2\*\*15 to 2\*\*0 of the OCP control register (working store X27).

### Image store write

The effect of a write is controlled by bits 2\*\*16 and 2\*\*17 of the operand. The combined values of these two bits have the following effect:

- 00 => Bits 2\*\*0 to 2\*\*15 of operand replace corresponding bits in the control register

- 01 => Bits 2\*\*0 to 2\*\*15 of operand are 'or'd into the control register

- 10 => Bits 2\*\*0 to 2\*\*15 of operand are cleared in the control register

- 11 => Illegal; gives program error 9, subclass 4

#### Meaning of bits in control register

2\*\*0 - Inhibit full photograph

2\*\*1 - Inhibit photograph

2\*\*2 - Not used

2\*\*3 - Inhibit data slaves

2\*\*4 - Not used

2\*\*5 - Inhibit retries

2\*\*6 - Not used

2\*\*7 - Inhibit hamming correction reporting

2\*\*8 - Not used

2\*\*9 - Pull HELP on program error

2\*\*10 - Stop on program error

2\*\*11 - Not used

2\*\*12 - Inhibit photo on soft system error

2\*\*13 - Retry in progress

2\*\*14 - Stop after photograph

2\*\*15 - Error handling in progress

R.D. Eager

16th August 1982

No: 2

Date: 15/12/77

#### ICL 2970 Engineer's Panels

The attached description of the 2970 Engineer's panels has been taken from two ICL technical documents (diagrams: 65/94562, text: 65/94563); it describes the <u>current</u> state of the panels, i.e. following the SML19 hardware upgrade.

The question of providing this information was raised originally by my receipt (via John Maddock) of a similar document produced by the Post Office, relating to the Barbican machine. A number of people using the 2970 expressed an interest in it. However, although the P.O. document contains a slightly fuller description of the handkeys and indicators than the attached note, it is now out of date as a result of SML19. Nonetheless, much of the information in it is still relevant to our 2970; I have kept it and can give anyone interested a listing. It has been filed as Hardware Note 2a.

I should like to thank Les Mowbray (ICL 2900 Engineer) and John Maddock for their help.

John M. Murison

Issue

#### 1 GENERAL LAYOUT

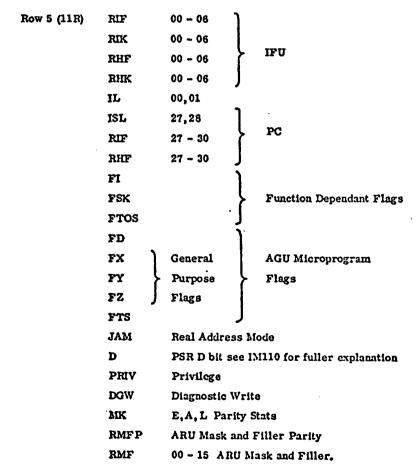

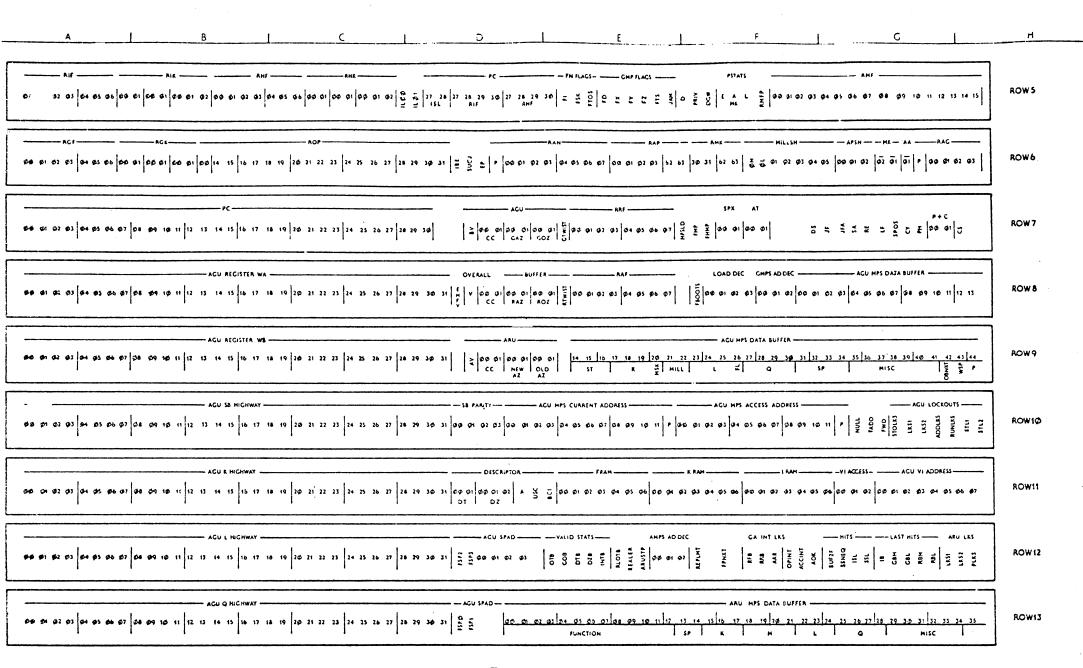

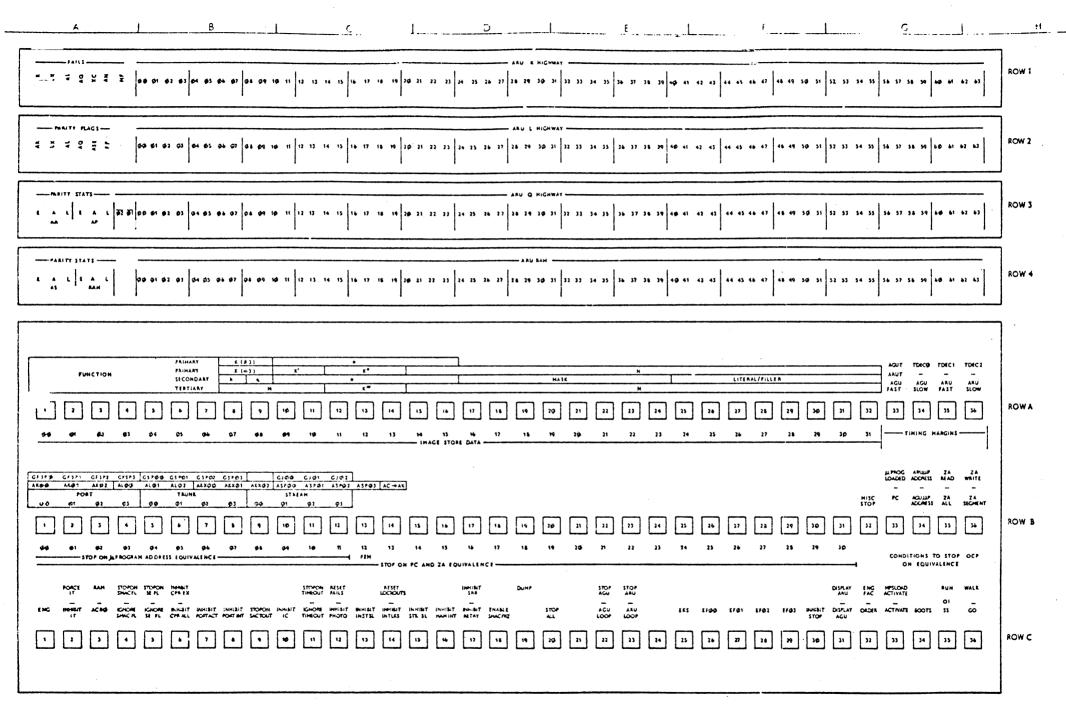

The OCP Engineer's facilities comprise 19 rows of monitor lamps with 72 lamps in each row & 1 row of monitor lamps with 36 lamps and 3 rows of handkeys with 36 in each row. The layout of handkeys and monitor lamps are shown on OD61 to 64 of document 65/94562 and their operational usage is described in the following text.

#### 2 MONITOR LAMPS (Brackets at row number indicate MDP socket)

- Row 1 (1R) The group of seven lamps at the left-hand end of this row display ARU Fails; AK, LX, AL, AQ, XC, AN and MF. The remaining lights display the ARU K highway (bits 00-63).

- Row 2 (2R) The ARU Parity Flags are indicated by the group of six lamps situated at the left hand end of this row; AK, LX, AL, AQ, ASE (Inhibit System Error), and FP (Force Parity error). The remaining lamps display the ARU L highway (bits 00-63).

- Row 3 (3R) The ARU AA and AP parity stats. (E, A and L) are displayed at the left hand end of this row. The remaining lamps are devoted to displaying the ARU Q highway (bits 2-63).

- Row 4 (4R) The ARU AS and RAM parity stats. (E, A and L) are displayed at the left hand end of this row, the remainder display the contents of the ARU Ram (00-63).

Issue

....... 02\ 24309

6

| Row 6 (12R) | RGF    | 00 - 06        | AGU Function Register                     |

|-------------|--------|----------------|-------------------------------------------|

|             | RGK    | 00 - 05        |                                           |

|             | ROP    | 00, 14 - 31    |                                           |

|             | IBE    |                | Instruction Buffer empty.                 |

|             | Sucj   |                | Jump condition satisfied.                 |

|             | EP     |                | Event pending                             |

|             | ran    | P. 00 - 07     | ARU AN register                           |

|             | RAP    | 00 - 03, 62,63 | ARU AP bits                               |

|             | RMK    | 30, 31, 62, 63 | ARU MK bits                               |

|             | Millsh | OM, OL, 01-05  |                                           |

|             | APSH   | 00-02          | AP shift                                  |

|             | MK     | 01, 02         |                                           |

|             | AA     | <b>51</b>      |                                           |

|             | RAG    | P, 00-03       |                                           |

| Row 7 (13R) | PC     | 00-30          | AGU PC                                    |

|             | BA     |                | AGU B Overflow.                           |

|             | CC     | 00;01          | AGU CC                                    |

|             | GAZ    | 00,01          | AGU ACC size.                             |

|             | GOZ    | 00,01          | AGU Operand size.                         |

|             | GTWIST |                | AGU TWIST stat.                           |

|             | RRF    | 00-07          | Buffer Function Register.                 |

|             | MPSLD  |                | Loading mps (HWW7 or overlay)             |

|             | PMP    |                | Microprogram loaded flag                  |

|             | FHMP   |                | Hardwired microprogram flag               |

|             | SPX    | 00,01          | ARU Scratchpad ext. bits                  |

|             | AT     | 00,01          | ARU Arithmetic type.                      |

|             | DS     |                | ARU Double/Single length shifting.        |

|             | JF     |                | ARU Jump Flag.                            |

|             | JFA    |                | ARU Jump Flag A                           |

|             | 8A     |                | ARU Address SPAD from AN.                 |

|             | RE     |                | ARU Register Extension                    |

|             | LF     |                | ARU Link register from microprogram bits. |

|             | SPOS   |                | ARU Sign Positive (Dec. arithmetic).      |

|             | CY     |                | ARU mill carry flag.                      |

|             | PM     |                | Program Mask (PSR)                        |

|             | P+C    | 00.01          | ARU Multiplier.                           |

|             | CS     |                | ARU Carry Save.                           |

|             |        |                |                                           |

| Row 8 (14R)  | WA          | 00-31           | AGU WA registor.                   |

|--------------|-------------|-----------------|------------------------------------|

|              | <b>EMFV</b> |                 | Emulation Floating point overflow  |

|              | V           |                 | Common overflow                    |

|              | CC          | 00,01           | Common CC                          |

|              | RAZ         | 00,01           | Buffer ACC size                    |

|              | ROZ         | 00,01           | Buffer Operand size                |

|              | ARUTWIST    |                 | ARU TWIST Stat.                    |

|              | RAF         | 00-06           | ARU Function Register.             |

|              | FBOOTS      |                 | Hardwired Bootstrap.               |

|              | LOAD DEC    | 00-03           | Direction bits.                    |

|              | GMPS AD I   | DEC 00-02       | AGU Microprogram Address selection |

|              | MPS DATA    | . 00–13         | AGU MPS Data Buffer (see Row 9).   |

| Row 9 (15R)  | WB          | 00-31           | AGU WB register.                   |

|              | ΑV          |                 | ARU Overflow                       |

|              | CC          | 00,01           | ARU CC                             |

|              | NEW AZ      | 00,01           | ARU New Instruction ACC size.      |

|              | OLD AZ      | 00,01           | ARU Previous Instruction ACC size. |

|              | MPS DATA    | 14-44           | AGU MPS Data Buffer.               |

| Row 10 (16R) | SB          | 00-31           | AGU SPAD output highway.           |

|              | SB          | P0-P3           | AGU SPAD output highway parity     |

|              | MPS CURF    | R ADD. 00-11, P | AGU Microprogram Current Add.      |

|              | MPS ACC     | ADD. 00-11, P   | AGU Microprogram Access Add.       |

|              | NULL        |                 | Null Beat (AGU)                    |

|              | FADD        |                 | Forced Address (AGU).              |

|              | FWD         |                 | •                                  |

|              | STOLK3      |                 | AGU Lockout.                       |

|              | LKS1        |                 | AGU Lockout.                       |

|              | LKS2        |                 | AGU Lockout.                       |

|              | ADD LKS     |                 | Ħ                                  |

|              | Run Lks     |                 | ti                                 |

|              | ST1.1       |                 | 19                                 |

|              | STL2        |                 | n                                  |

| Row 11 (17R) | к           | 00-31           | AGU K highway.                     |

|              | DT          | 00,01           | Descriptor Type.                   |

|              | DZ          | 00-02           | Descriptor Size.                   |

|              | A           |                 | A bit,                             |

|              | USC         |                 | Unscaled.                          |

|              | BCI         |                 | Bound Check Inhibit.               |

|              | FRAM        | 00-06           | Function RAM Addressing.           |

|              | KRAM 00-06       | K Field RAM Addressing.                  |

|--------------|------------------|------------------------------------------|

|              | IRAM 00-06       | Descriptor RAM Addressing.               |

|              | VI Access 00-02  | Volatile Index Address Selection.        |

|              | VI ADD 00-07     | Volatile Index Addressing.               |

| Row 12 (18R) | L 00-31          | AGU L highway.                           |

|              | FSP 2 & 3        | AGU SPAD Flags.                          |

|              | SPAD ADD 00-03   | " " Addressing                           |

|              | ОТВ              |                                          |

|              | GOB              | Valid Stats. (Microprogram Address valid |

|              | DTB              | for replaced jumps if required).         |

|              | DZB              |                                          |

|              | INTB             |                                          |

|              | RLOTB            |                                          |

|              | REALER           |                                          |

|              | ARUSTP           |                                          |

|              | AMP AD DEC 00-02 | ARU Microprogram Address selection.      |

|              | REPLMT           |                                          |

|              | FPNXT            | Next ARU func. is floating point.        |

|              | RFB              | AGU/ARU Interlocks.                      |

|              | RBB              | tt ti                                    |

|              | AAR              | 69 61                                    |

|              | OPINT            | Operand in Internal Format.              |

|              | ACINT            | ACC in Internal Format.                  |

|              | AOK              |                                          |

|              | BUF 2F           | Association Address                      |

|              | SSNEQ            | Stack Segment Number Equivalence         |

|              | ISL              | Instruction Slave Slave hit              |

|              | SSL              | Stack slave                              |

|              | .IB              | j                                        |

|              | GBM<br>GBL       | 1                                        |

|              | RBM              | Slave last hit                           |

|              | RBL              |                                          |

|              | 97-2-2           | J                                        |

|              | LKS 1            | ARU Lockout.                             |

|              | LKS 2            | ч                                        |

Pipe Locks

PLKS

#### 2970 OCP ENGINEERS FACILITIES

Number 65/94563

Sheet

Issue

Row 13 (19R) 00-31 AGU Q highway. FSP0 & 1 AGU SPAD Flags

> MPS 00-35

ARU Microprogram word.

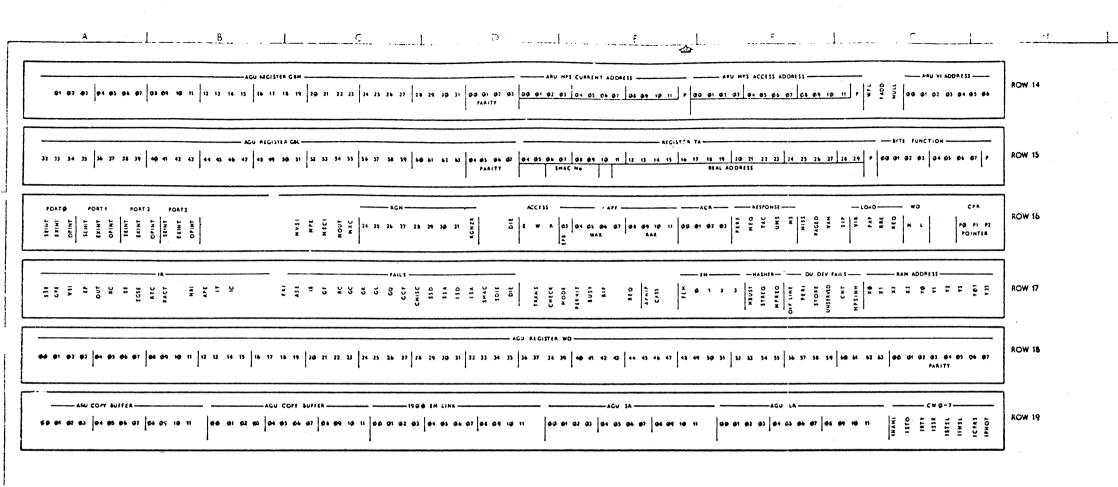

00-31, 0P-3P Row 14 (20R) GBM AGU GB Most.

> MPS CURR ADD 00-11, P ARU Microprogram current address.

> MPS ACC. ADD 00-11, P ARU Microprogram Access address.

ARU Wait for Literal. WFL ARU Forced Address. FADD

ARU Volatile Index Address. VIADD 00-06

Row 15 (21R) GBL 32-63 AGU GB Least.

AGU GB Least Parity GBL 04-07

> Store Address, (Real Address). 04-29, P

BYTE FUNC 00-07, P

Row 16 (22R) PORT 0 SEINT

PORT 0 EXINT

PORT 0 OPINT

PORT 1 SEINT

PORT 1 EXINT

PORT 1 OPINT

PORT 2 SEINT

PORT 2 EXINT

PORT 2 OPINT

PORT 3 SEINT

PORT 3 EXINT

PORT 3 OPINT

Direct wired interface interrupts.

MVSI Masked Virtual Store Interrupt.

MPE Masked Program Error.

MSCI Masked System Call Interrupt.

MOUT Masked Out Interrupt.

MXC Masked Extracode.

RGN 24-31 AGU GN

RGNZR AGU GN bits 8-23 = zero.

Issue

**Row 16** Cont.

ACCESS E Store Access Execute. **ACCESS W** Store Access Write. ACCESS R Store Access Read. APF 03-11 Access Protection Field bits. ACR 00-03 Access Control Register. PERF Permission Fail. MEQ Multiequivalence. TAC ATU Accept (Hit). UMS Update Miss (Use bits). MS Miss. MISS PAGEI Paged segment address. VAM Virtual Address Mode. SIP Search In Progress (TS). LOAD VIR Load Virtual Address. LOAD PAP Load Page and Permission bits. LOAD RRE Load Real Even address. LOAD REO Load Real Odd address.

CPR P0-P2 ATU CPR Pointer.

Row 17 (23R) SSE

GPE

WD M, L

VSI

EP

OUT

XC

SE

SGSE

RTC

XACT HRI

APE

IT

IC

Interrupt Register

11

Issue

**Row 17** Cont.

Function K and Indirect RAMS FKI ASE **ARU** System Error İB Instruction Buffer RC ARU control AGU control GC K highway GK L highway GL GQ Q highway GCY **Carries** AGU Misc. **GMISC**

Stack Slave Data

Stack Slave Address

Instruction Slave Data.

Current stats. of ATU

Instruction Slave Address

Parity Fail Stats.

SMAC

SSD

SSA

ISD

ISA

SDIE Software DIE Hardware DIE DIE

TRANS CHECK

MODE

PERMIT

BUSY RIP REQ

**АРНІР** ARU Photograph in Progress

**CASS** Cassette is Busy Emulation mode flag. FEM EM 0-3 Emulation mode. Hash Busy H BUSY

STREQ Store Request Microprogram request **MPREQ**

OFFLINE

PERI Perifail STORE Store Fall

UNSERVED

CNT MPSINII

Requests from input device to main and Microprogram store,

Diagnostic Unit Input Device Fails

RAM Add, X0-3

Y0-3 Y01,Y23 ATU RAM Address.

MPS Inhibit Fai.

Count Fail

ACR use bit checks RAM address since only one ACR use bit is held for each Virtual Address

Pair (even and odd).

CW

STATS

4

| Kow 18 (24R) | WD | 00-63, P0-P7 | Write Buller store. |  |

|--------------|----|--------------|---------------------|--|

|              |    |              |                     |  |

|              |    |              |                     |  |

Row 19 (25R) ARU COPY BUFFER 00 - 11 AGU COPY BUFFER 00 - 11

> 1900 EM LINK 00 - 11 1900 Emulation Link (AGU) 00 - 11 AGU SUBROUTINE **AGU SR**

AGU LR 00 - 11 AGU Link Inhibit Hamming Interrupt INHAM

INSTO Inhibit Main Store IRTY Inhibit Retry

Inhibit Successful Retry Reporting **ISRS**

Inhibit Stack Slave ISTSL Inhibit Instruction Slave IINSL

Inhibit Current page/segment Registers **ICPRS**

Inhibit Photo IPHOT

#### External Monitor Strip

Peripheral Interrupt OPTINT 0,1

IDLE

OPERAND 14-31

HMP Hard Microprogram

**GMPADD** 8-11 **AGU** Microprogram Address SEINT 0,1 System Error Interrupt

**SMACFL** SMAC Fail

Issue

#### HANDKEYS

The handkeys are arranged in three rows A, B and C and are depicted on OD61 of document 65/94562.

Row A Handkeys 1 - 32 are used for setting up Image Store data.

Handkeys 33 - 36 vary the OCP Timing Margins as follows:

| <b>a)</b> | Key 33 | AGU FAST down - All AGU timing speeded up by 5%      |

|-----------|--------|------------------------------------------------------|

| b)        | Key 34 | AGU SLOW down - All AGU timing slowed down by 20-25% |

| c)        | Key 35 | ARU FAST down - All ARU timing speeded up by 5%      |

| ď)        | Key 36 | ARU SLOW down - All ARU timing slowed down by 20-25% |

Note: The results of setting AGU FAST and AGU SLOW or ARU FAST and ARU SLOW is indeterminate.

- e) All four switches in centre position timing at nominal speed.

- f) Key 33 up Individual AGU timing pulses as determined by a decode of the remaining 3 switches speeded up by a constant 5 n Sec (see table 1).

| Switches |                    |        | AGU Timing Pulse      |

|----------|--------------------|--------|-----------------------|

| KEY 34   | KEY 35             | KEY 36 | Speeded up by 5n Sec. |

| Centre   | Centre             | Centre | T08TM                 |

| Centre   | Centre             | TDEC2  | T14TM                 |

| Centre   | TDEC1              | Centre | . <b>T17TM</b>        |

| Centre   | Tu <sub>E</sub> C1 | TDEC2  | TI9TM                 |

| TDEC0    | Centre             | Centre | T12DF                 |

| TDEC0    | Centre             | TDEC2  | T12TM                 |

| TDEC0    | TDEC1              | Centre | T17GMIL               |

| TDEC0    | TDEC1              | TDEC2  | Conditional Jump      |

Table 1. AGU timing Pulse Margin Speed Up

g) Key 33 centre - Individual ARU timing pulses as determined by a decode of the remaining 3 switches speeded up by a constant 5n Sec (see table 2).

Number 65/94563

Sheet 14 Issue

4

| Switches |        |        | ARU Timing Pulse               |

|----------|--------|--------|--------------------------------|

| KEY 34   | KEY 35 | KEY 36 | Speeded up by 5n Sec.          |

| Centre   | Centre | Centre | All AGU and ARU Timing Nominal |

| Centre   | Centre | TDEC3  | T11DF                          |

| Centre   | TDEC1  | Centre | T10TM                          |

| Centre   | TDEC1  | TDEC3  | TOSRTIM                        |

| TDEC0    | Centre | Centre | <b>T12</b> TIM                 |

| TDEC0    | Centre | TDEC3  | T12RTIM                        |

| TDEC0    | TDEC1  | Centre | T17RTIM                        |

| TDEC0    | TDEC1  | TDEC3  | T17MILL                        |

ARU Timing Pulse Margin Speed Up Table 2.

15

Issue

4

Row B This row of keys enables the OCP to stop on a specified address, stopping on either microprogram equivalence (handkeys 1 - 12) or, on PC and ZA equivalences (keys 1 - 31). The specific equivalence on which the OCP stops is determined by the four keys situated at the extreme right-hand end of this row (keys 33 - 36).

MISC STOP, Key 32 down, stops the OCP when the AGU Miscellaneous Function 'STOP ON MISC' is set.

Stop on Microprogram loaded/PC; Key 33 enables the OCP to be stopped when the microprogram has completed loading by detecting #F (Stop character) in the direction bits. The other position of the key "Stop on PC equivalence" stops the OCP immediately equivalence is detected between the bits set-up on the handkeys and PC providing that "Stop on AGU/ARU Microprogram address" is not set. The OCP will resume running when the key is returned to the centre off position.

Stop on - ARU/AGU microprogram address; Key 34 enables the OCP to be stopped when bits 00-11 of the ARU/AGU microprogram address are equal to the bits set up on the keys. The OCP will resume running when the handkey is returned to its centre-off position.

When both the "Stop on PC" Keys 13-31 and "Stop on AGU microprogram address" 1-12 are set, then the OCP will only stop when equivalence is detected between these conditions and that set up on the keys.

ZA Read/ZA All and ZA Write/ZA Execute; Keys 35 and 36 enable the OCP to be stopped when ZA (which normally contains the virtual address) is equal to the bits set on the keys. The OCP will resume running when the appropriate key is returned to its centre-off position.

Keys 1 - 12 can also be used to set up the Port, Trunk and Stream when doing a Bootstrap or dump (Row C handkey 34).

FEM, Key 13 down, stops on selected address (Keys 1 - 12) when in emulation mode and stops on selected address in normal mode when key in neutral position.

A further facility exists on this row in that the group of keys at the left-hand end can be set to force either the ARU K (AK 00-02) L (AL 00-02) and KX (AKX 00-02) highways and the ARU scratchpad (ASP 00-03) and AC — AK, or alternatively the AGU Scratchpad Flags (0-3) and AGU Scratchpad, and J Highway. The condition to be displayed is dependant upon the setting of the Display ARU/ Display AGU handkey (key 31 Row C).

110111201 03/34303

#### Row C

KEYS

| 1 ENG                              | Enables Engineers panel and disables OPER                                                                      |

|------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 2 FORCE IT INHIBIT IT              | Force Interval Timer interrupt                                                                                 |

| INHIBIT IT                         | Inhibits interrupts from the Interval Timer and RTC                                                            |

| RAM                                | Force Real Address Mode                                                                                        |

| 3 { RAM<br>ACRO                    | Force ACR0                                                                                                     |

| 4 STOP ON SMAC FL IGNORE SMAC FL   | Allows OCP to stop on unrecovered SMAC Fails Allows OCP to ignore unrecovered SMAC Fails                       |

| STOP ON SE FL                      | Stops OCP on System Error Fail                                                                                 |

| 5 STOP ON SE FL IGNORE SE FL       | Allows OCP to ignore System Error Fail                                                                         |

| 6 { INHIBIT CPR EX INHIBIT CPR ALL | Prevents the CPR's being used during execute accesses  Prevents the CPR's being used during all store accesses |

| 7 { INHIBIT PORT ACT               | Prevents the OCP from taking any action as a result of receiving an ACTIVATE                                   |

| 8 { INHIBIT PORT INT               | Prevents the OCP from raising an interrupt as a result of receiving a port interrupt.                          |

| s { STOP ON SACTOUT                | Causes OCP to stop on SAC Time out                                                                             |

| 10 { INHIBIT                       | Inhibits the instruction counter interrupts                                                                    |

| 11 STOP ON TIMEOUT IGNORE TIME OUT | Causes OCP to stop on any time out                                                                             |

| TIME OUT                           | Allows OCP to ignore any time out                                                                              |

KEYS

| 12 RESET FAILS INHIBIT PHOTO     | Resets any outstanding fail Allows the system Error Interrupt routine to omit the Photo of the OCP hardware                                     |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 { INHIBIT INSTSL              | Inhibits the Instruction slave                                                                                                                  |

| 14 RESET LOCKOUTS INHIBIT INTLKS | Reset any Lock outs (or any timing interlocks) Allows AGU and ARU to run irrespective of any interlocks that may be set.                        |

| 15 { INHIBIT STK SL              | Inhibits the Stack Slave causing all read accesses to come from main store.                                                                     |

| 16 { INHIBIT HAM INT             | Inhibits any Hamming Interrupt                                                                                                                  |

| 17 { INHIBIT SRR INHIBIT RETRY   | Inhibits successful Retry reporting  Allows the system Error Interrupt to by pass the hardware retry.                                           |

| 18 ENABLE SMAC FRZ               | This key allows the OCP general reset (FREEZE) to be passed via a Port to the SMAC.                                                             |

| 19 { DUMP                        | Results in a PAW Function of Dump being sent to the Controller selected on the Keys of Row B when the RUN Key (35 Row C) is set OCP then stops. |

| _                                |                                                                                                                                                 |

Allows Stop on nulls (AGU and ARU)

Stop AGU Clocks.

Stop ARU clocks.

Inhibits the strobing of the AGU microprogram data buffers, thus

Inhibits the strobing of the ARU microprogram data buffers thus

enabling a specific beat to be repeated indefinitely.

enabling a specific beat to be repeated indefinitely.

Number 65/94563

Sheet 18

Issue

This key is the M.S.B of the Engineers Facility Field and also the drop through Idle

26-29

These keys have two functions:-

- (X) They are looked at, at Microprogram load time (IPL), and if the decode is #5, the VAR Register is loaded from the Image Store Keys Row A.

- (Y) These four Keys and EKS (Key 25) provide a means of forcing several functions manually provided the Engineers facility (Key 32 Row C) is operated. The OCP should be at Real OTB. Key 35 Row C should be in OI position. The Engineers facility is performed by setting the decode, then pressing and releasing the Engineers Facility Key (Key 32 Row C), followed by the operation of the GO Key (Key 36 Row C).

The facilities provided are as follows:-

Engineers Facilities.

No Action

PC JUMP

Jump to Address on Image Store data keys Row A as peraddress mode, Virtual or Real.

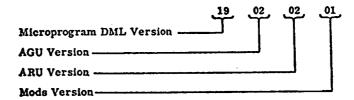

**MPVERS**

Microprogram Version displays on the AGU Register WB display on Row 9. The decode is Hexadecimal. For example:

3-7

No Action.

READ

Read from virtual address in Store.

The address is set on Image Store Keys Row A.

The information read is displayed in Registers GBM and GBL Rows 14 and 15.

140111061 09/3/1909

Sheet

19 Issue

| 9  | READ +              | Read from virtual address is store. The address is set on Image Store Keys Row A. The information read is displayed in Registers GBM and GBL Rows 14 and 15. EKS key being pressed and released increments the virtual address by 2 words and the new information is displayed in GBM and GBL Registers. The microprogram can be returned to real OTB by returning EF 00-03 keys to neutral and pressing and releasing EKS Key.                                                                                     |

|----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A  | Read R+             | As 8 (READ) but the Real Address Mode Key (Key 3 up Row C) operated.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| В  | Read R +            | As 9 (READ +) but the Real Address Mode Key (Key 3 up Row C) operated.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| С  | WRITE               | Write to the virtual address set on the Image Store Keys Row A upon the operation of the GO Key (Key 36 Row C). The machine will now wait for data to be set on the Image Store Keys. When EKS Key is operated this data is written into the virtual address in store                                                                                                                                                                                                                                               |

| D  | WRITE +             | Write to the virtual address set on the Image Store Keys Row A upon the operation of the GO Key (Key 36 Row C). The machine will now wait for data to be set on the Image Store Keys. When EKS key is operated this data is written into the virtual address in store. Further press and releases of the EKS key increment the address by 2 words and write the data on Image Store Keys. The microprogram can be returned to real OTB by returning EF00-03 keys to neutral and pressing and releasing the EKS key. |

| E  | WRITE R             | As C but Real Address Mode key operated (Key 3 up Row C).                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| F  | WRITE R+            | As D but Real Address Mode key operated. (Key 3 up Row C).                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10 | MOVEOVER            | Move overlays from existing to new area of store set on Image Store keys (Row A).                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11 | FOTO                | Force Photo, done automatically by this key.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12 | READ INST<br>SLAVE  | Read the line of the Instruction Slave defined on Image Store Keys, and appears on monitor lights GBM and GBL Rows 14 and 15.                                                                                                                                                                                                                                                                                                                                                                                       |

| 13 | read stack<br>Slave | Read the line of the Stack Slave defined on Image Store Keys, and appears on monitor lights GBM and GBL. Rows 14 and 15.                                                                                                                                                                                                                                                                                                                                                                                            |

No Action.

14,15

Sheet Issue

20

16 READ AND WRITE SAC AND SMAC I.S. To read set the Engineers Facility keys, set the image store address as defined below .. and perform the functions described in paragraph (Y). preceding the Engineers Facilities. The information in GBM is the Image Store address which has been set up and in GBL is the information Read.

To Write set up Image Store Keys Row A, perform the Engineers Facility operation described in paragraph (Y) but after the GO key has been pressed the OCP will wait for data which is to be set up on Image Store Keys. EKS key is pressed and released this causes the Image Store write action to be completed.

Image Store Keys Row A.

Bit 0:- 0 Read, 1 Write

4.5:- Both down :- SMAC; 5 only :- SAC; No keys operated:- SAC Trunk.

SMAC

Bits 8-15 SMAC number

Bits 16-31 SMAC Image Store Address

(see N. R. S. D 4, 2, 3 G)

SAC

Bits 8-11 Port number of SAC

Bits 16-31 The Image Store Address

17 No Action

WRITE SPADS 18

On image Store keys 24-27 put the S. P. Flags, and on keys 28-31 put the S. P. line number. The Image Store Engineers Facility action described in paragraph (Y) is performed. The data to be written to the Scratch Pad is set on the Image Store Keys. EKS key is then pressed and released.

19 **UPDATE SP**  This updates the visible Registers to the current machine state automatically

e.g. ACS, CC, OV in PSR

SP SA (IT Copy)

SP PC

SP SW (A0 Copy)

SP SD (IC Copy)

SP SX (A1 Copy)

SP SY (A2 Copy)

SP SZ (A3 Copy)

Issue

Used in conjunction with stop keys to provide Engineers Scope trigger.

DISPLAY

This key causes the Register(s) selected by the keys on row B to be placed on the highways which in turn are displayed on monitor lamps.

Enables the Five Keys 25-29.

The ORDER position allows the primitive interface order set up on ROW A to be obeyed. If only one order is required the RUN key (35 Row C) is placed in the appropriate position and the GO Key is pressed once.

33 MPSLOAD ACTIVATE When operating the MICROPROGRAM LOAD switch it is assumed that the microprogram is in the main store starting at #100 BYTES, the RUN switch (Key 35) should also be set. The microprogram is then loaded and entered and if it is a normal Microprogram it carries out a register load from #80 BYTES etc.

33 ACTIVATE The ACT position of this switch causes an entry to the microprogram such that if a normal microprogram is in, a register load from \$80 BYTES etc. is carried out when RUN is set.

Operation of this key results in a PAW function of IPL being transmitted to the controller selected by the Keys of Row B. On receiving an interrupt from the controller the OCP loads its microprogram

RUN 35

The RUN position allows the clock to run until it is stopped by a stop condition or RUN is switched off. The conditions for stopping are various and are as follows.

- 1. The stop conditions described under ROW B

- 2. System error with stop on System Error or system Error mask set.

- Inhibit time out and the OCP is waiting for something.

- AGU and ARU only with the interlock functioning.

35 OI One instruction allows a single instruction for each operation of WALK/GO key.

35 **S3**  Single shot allows a single microprogram instruction for each operation of WALK/GO key.

Issue

22

A 16  $\mu$  sec clock used in conjunction with OI and SS.

A Single Shot used in conjunction with OI and SS.

| OPINT |                                                        | - GMMOD SEINT |  |

|-------|--------------------------------------------------------|---------------|--|

| • •   | 0 14 15 46 17 16 M 29 21 22 23 24 25 26 27 28 29 30 31 | H H H H H H   |  |

No: 3

Date: 13/12/79

#### How to Force a Program Error Interrupt from the Handkeys

Before a dump can be usefully taken the machine must be at IDLE "DEAD". This state is reached after most hardware and software errors. However, if the machine is not at IDLE "DEAD" an error should be forced, as follows:

#### For the 2960 (SM11, using TLOE/8):

On the ECP, type:

DW 9FFC WMA 0 E GO

#### For the 2970:

- 1. Off "RUN"

- 2. "ENG" down

- 3. Handkeys (top row) to ZERO

- 4. One tick on "GO" (usually, but more ticks may be necessary) until the RLOTB light comes on

- 5. "ORDER" down

- 6. Press "GO" until no lights on in RGF (2nd row of lights from top)

- 7. "ORDER" central

- 8. "RUN" machine goes to IDLE "DEAD"

#### For the 2980:

1. Set switches as follows:

| SMGO                                | UP      | (Row 1 Key 1) |

|-------------------------------------|---------|---------------|

| S.INST.MODE followed by S.SHOT MODE | DOWN/UP | (Row 6 Key 2) |

| Il STOP                             | DOWN    | (Row 3 Key 7) |

| STOP ON FAIL                        | UP      | (Row 5 Key 4) |

| INH.ORD.STOP                        | DOWN    | (Row 5 Kev 9) |

These are the only switches that should be set, apart from the deck TRUNK/STREAM switches. Unset any others.

- 2. Turn to Frame Ol (Critic and Modifier Dataflow) on monitor display.

- 3. Set Serial Monitoring address keys to Frame 1, Line 3.

- 4. Set bit 17 on DATA-KOD keys.

- 5. Press SET REG (Row 1, Key 4 UP). Check that lamp FSEI on Line 3 (bit 17) comes on.

- 6. Turn to Frame 10 (Modification and B Arithmetic Stage Microprogram) on monitor display.

- 7. Set RUN (Row 6, Key 2 CENTRAL).

- 8. Press GO (Row 6, Key 1 DOWN). Check that machine stops with II (Line 7, bit 4) lamp lit.

- 9. Turn to Frame 21 (SAC trunk links E, F, G, H) on monitor display.

- 10. Rest Il STOP (Row 3, Key 7 CENTRAL).

- 11. Press GO (Row 6, Key 1 DOWN) machine goes to IDLE "DEAD".

R.D. Eager J.F. Livingstone P.D. Stephens J.K. Yarwood

No: 4

Date: 19/12/77

#### Hardware Testing

A process, ENGINR, exists to be used for running hardware tests. Currently two tests exist:

a) A test of the VMY instruction accessing the B register and data which goes across a page boundary. This used to give an erroneous bound check on the 2970 when a page fault occurred during its execution; it has now been corrected. The test is preserved for use on other 2900 machines. To run it, type:

COMMAND: RUN VMYBY

DO YOU WANT SECOND PAGE IN CORE?

Y/N: N or Y

VMY B WORKED OK.

Note that the program should work whether or not the second page is in core. If the fault exists the program will work when the reply is 'Y', but will fail with a band check if the reply is 'N'.

#### b) RAND READ

This is a program based on RAND READ on System 4 EMAS. It can be used to test up to 4 disk drives. The disks are referred to by their FSYS numbers - e.g. PETEO1 is disk 1, EMAS10 is disk 10.

The program is run thus:

COMMAND . RANDREAD

NO OF DISKS:

reply 1-4

FSYS NOS. OF DISKS: reply with FSYS numbers

Q SIZE PER DISK:

reply 1-16, specifying number of transfers to

be PONned to each disk at once

READS/DISK:

reply with number of READs to be done

When the specified number of reads have been completed, the number of faults, cumulative since the start of the command, are reported and the user is then invited to continue. The reply should be Y to continue or N to stop the tests. If the user replies with Y, the READS/DISK: prompt is given again; the other parameters are held at their previous values.

No: 5

Date: 27/1/78

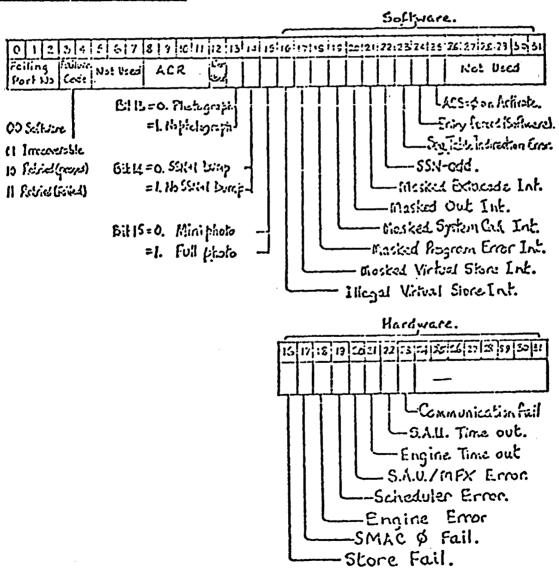

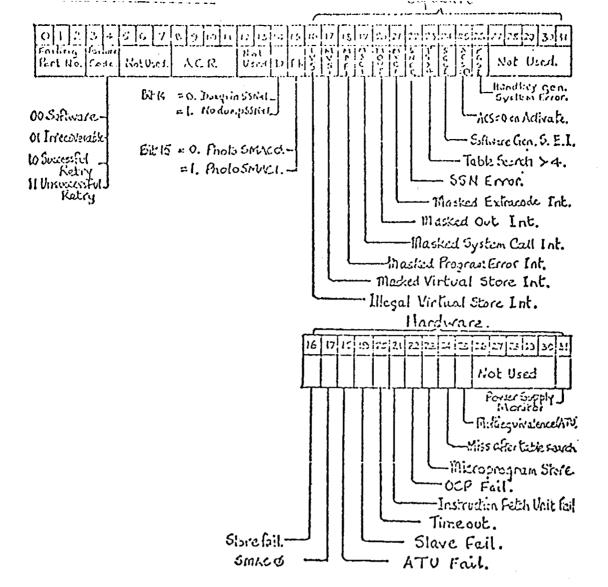

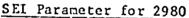

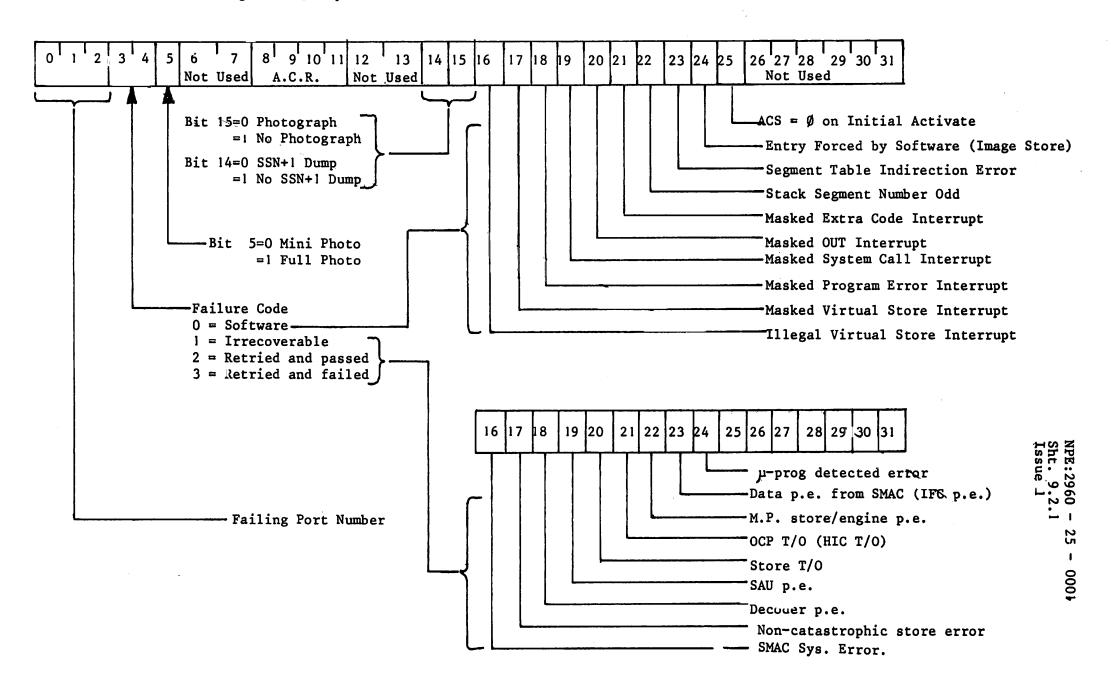

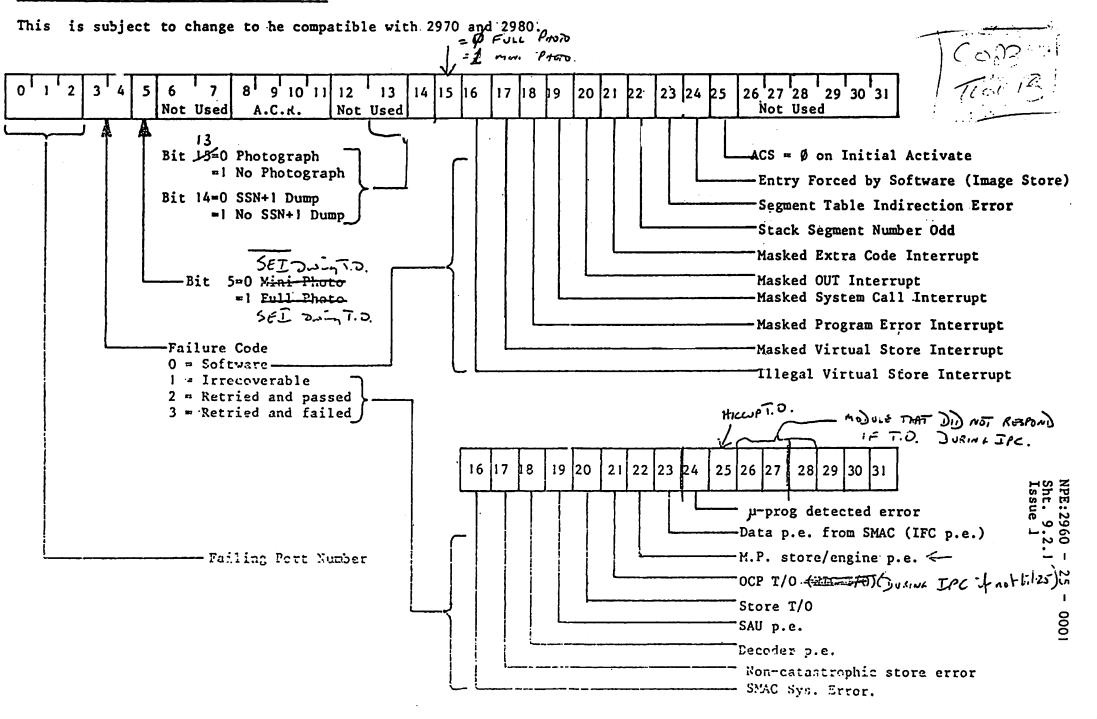

# System Error Interrupt Parameters for 2960, 2970, 2980

This note is taken from a badly-Xeroxed copy of ICL document SYSB-22-0233.

#### The System Error Interrupt Stack

The system error is a stack switching interrupt and the code of SEI Analyser is entered with its LNB at the stack base. Word 0 contains the stack segment number (in the current implementation this is public segment 8198). Words 1 and 2 are zero and words 3 and 4 point to the Procedure Linkage Table (PLT) of the compilation module containing SEI Analyser. Word 5 contains the SEI parameter as stacked by the hardware interrupt routine and word 6 is the segment number of the interrupted stack.

#### SEI Parameter for 2960.

The parameter for interrupts other than on the current OCP port will look like an empty software failure parameter (i.e. bits 16-31 not used).

No: 6 Date: 11/7/78

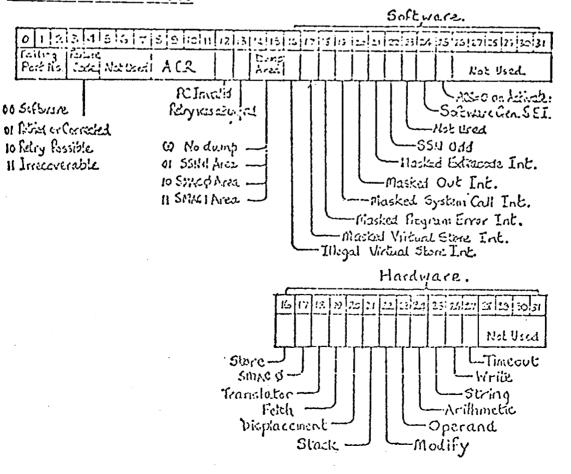

#### 2970: How to Reconfigure the Store on a SMAC

Use the bottom row of (mostly) blue keys in the store cabinet:

The BLOCKO NUMBER key is grey, all other keys on this row are blue. Each 128 Kb block required to be on-line should have its corresponding key (0-15) pressed down. Effect the reconfiguration by pressing (and releasing) the adjacent BLOCK CONFIG key. The BLOCKO NUMBER refers to the lowest numbered on-line block (generally real block 0). If the reconfiguration changes the lowest numbered block then the new BLOCKO number should be set on the four grey keys on the row above the block configuration row and the BLOCKO NUMBER key pressed and released. The fifth row of lights on the Store cabinet displays the current block configuration and BLOCKO number.

N.B. The Store need not be contiguous <u>except</u> that the EMAS Supervisor loader requires blocks 0 and 1 of SMAC 0 to be configured on-line.

John Maddock

No: 7

Date: 9/10/78

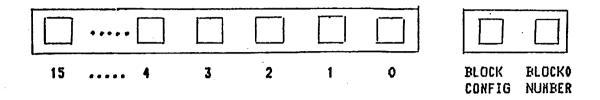

# 2950: Notes on Transfer Control Blocks (TCBs) for People Who Are Used to the GPC

This Note is intended as a commentary on pages 30-40 of the ICL Product Specification document PSD 2.5.3, an extract of which is available on request. The diagram is taken from the document.

#### TCB Word 0

| bits 0,1   | not used                                                                                                                              |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 2      | if set, suppresses termination on "attention"                                                                                         |

| bit 3      | not used                                                                                                                              |

| bits 4-7   | suppress long block, short block, condition X, condition Y = bits 8 to 11 of logic block entry                                        |

| bit 8      | data recharge from next TCB: equivalent to bit 4 of LBE                                                                               |

| bit 9      | inhibit interrupt: converse of bit 3 (PCI) in LBE (could also serve for bit 2 of SAW flags in STREAM SAW in H/W comm. area)           |

| bits 10-14 | not used                                                                                                                              |

| bit 15     | command qualifier: 0 for "device", 1 for "stream"; same as bit 15 in LBE (?)                                                          |

| bit 16     | preamble valid: controls initialisation, like RCB word 0 bit 16                                                                       |

| bit 17     | postamble valid: controls collection of status after unsuccessful transfer                                                            |

| bits 18,19 | not used                                                                                                                              |

| bits 20,21 |                                                                                                                                       |

| bit 22     | for read commands: don't write data to store (skip). ? Not same as LBE bit 2.                                                         |

| bit 23     | not used                                                                                                                              |

| bit 24     | output (this seems to be nonsense, except for stream commands)                                                                        |

| bits 24-31 | command (in actual fact bit 31 seems to signal 'output'). Whichever bit actually indicates 'output' should correspond to bit 0 of LBE |

#### TCB Word 1

| bits 0-3<br>bits 4-28 | not used copied from 2nd word of STE of data segment - real address of segment or page table |

|-----------------------|----------------------------------------------------------------------------------------------|

| bit 29                | not used                                                                                     |

| bit 30                | paged (same as bit 1 in 1st word of STE)                                                     |

| bit 31                | fixed - copied from 2nd word of STE; must be 1, unless you                                   |

|                       | have a command to transfer no data - then it must be 0                                       |

This substitutes for the sort of information which is found in word 1 of  $\ensuremath{\mathsf{RCB}}$ .

#### Notes

- (i) Shaded areas are ignored by IO System but those in word O are reserved (for hardware use).

- (ii) Word 0 must be on 2 word boundary in a Public Segment with the TCB in a contiguous area not crossing a page boundary.

The Transfer Control Block.

### TCB Words 2 and 3

Data descriptor. Must be a byte or string descriptor. Only the bound and address-within-segment are significant, and only 16 bits of the bound are used - i.e., byte count in word 2 bits 16-31, and address in word 3 bits 14 to 31. A zero byte count is taken to mean 2\*\*16. S/w should have word 2 bit 15 =1 in that case, and =0 in all others. Word 2 bit 5 must be set for "backwards" transfers (? corresponds to bit 1 of LBE).

These two words correspond to the address list entry.

## TCB Word 4

Public virtual address of next TCB - only bits 0 and 14-28 are significant. Bit 0 must be 1 (public address). If it is zero (local address) the chain is terminated. Therefore this corresponds to bit 4 V bit 5 in LBE (data chain V command chain). Only address-within-segment (bits 14-28) is significant because new TCB must be double word aligned and in same segment as previous TCB.

## TCB Word 5

bits 0-7 stream primary status

≡ bits 16-23 of word 0 of STREAM RESPONSE in Controller H/W

Comm. Area

bits 8-13 response flags

bit 8 stopped

bit 9 continued

bit 10 initialise failure

bit 11 sense failure

bits 16-31 remanent byte count

= bits 14-31 of word 1 of STREAM RESPONSE

#### TCB Words 6-9

## Preamble area

word 6 initialise data (among other things) ≡ word 6 of RCB

## TCB Words 10-13

Postamble area. Gets sense bytes - secondary and tertiary status bytes.

J. Wexler

## 2960 5TEM ERROR INTERRUPT PARAMETER

This is subject to change to be compatible with 2970 and 2980.

## 2960 SYSTEM ERROR INTERRUPT PARAMETER

## FIXED LOCATIONS IN WORKING STORE (N.R.)

a) Range Defined Registers Addr. by A/- or I/-

| Words Ø.1 | ACC ( | Ď |

|-----------|-------|---|

| 2.3       | ACC   | l |

| 4.5       | ACC 2 | 2 |

| 6.7       | ACC : | 3 |

| 8.9       | DR (  | Ď |

| 10.11     | DR :  | ı |

| 12.13     | SF    |   |

| 14.15     | В     |   |

36 (<del>//</del>24) ·

37 (#25)

b) Registers Addr. by C/- or C/B (For these C = # 10)

| Addr. | 16 | ( <del>//</del> 1Ø)  |      |        | Reg. |       |                           |

|-------|----|----------------------|------|--------|------|-------|---------------------------|

|       | 17 | ( <del>//</del> 11)  | Prog | Status | Page | PSR   | (also STACK #IE)          |

|       | 18 | ·( <del>//</del> 12) |      |        | Ü    | XNB   |                           |

|       | 19 | ( <del>//</del> 13)  |      |        |      | SSR   |                           |

|       | 20 | ( <del>//</del> 14)  |      |        |      | SSN   |                           |

|       | 21 | ( <del>//</del> 15)  |      |        |      | LTB   |                           |

|       | 22 | ( <del>//</del> 16)  |      |        |      | MBI   | (DETAIL SEE 3.7.3)        |

|       | 23 | ( <del>//</del> 17)  |      |        |      | RTCX  |                           |

|       | 24 | ( <del>//</del> 18)  |      |        |      | IRS   | (Int Reg)(DETAIL 3.7.4)   |

| Block | 25 | ( <del>//</del> 19)  |      |        |      | PAR ( | Parameter)                |

| Blech | 26 | ( <del>//</del> 1A)  |      |        |      | LSTB  | ø                         |

|       | 27 | ( <del>//</del> 1B)  |      |        |      | LSTB  | 1                         |

|       | 28 | ( <del>//</del> 1C)  |      |        |      | IMI   | (Int. Mask)               |

|       | 29 | ( <del>//</del> 1D)  |      |        |      | IM2   | (Commissioning INT. Mask) |

|       | 30 | ( <b>≠</b> 1E)       |      |        |      | PSTB  | ø                         |

|       | 31 | ( <del>//</del> 1F)  |      |        |      | PSTB  | 1                         |

|       | 32 | ( <del>//</del> 20)  |      |        |      |       |                           |

|       | 33 | ( <del>//</del> 21)  |      |        |      |       |                           |

|       | 34 | ( <del>//</del> 22)  |      |        |      | SI P  | AR                        |

|       | 35 | ( <del>//</del> 23)  |      |        |      | SIV   |                           |

|       |    |                      |      |        |      |       |                           |

DPC

RPAR

NPE:2960 - 25 - 0001 Sht. 3.7.2 Issue 1

## FIXED LOCATIONS IN WORKING STORE (CONT.)

| Addr.                       | 38 (#26)                                                                                   | Reg. HANDKEYS                                           |

|-----------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                             | 39 ( <del>//</del> 27)                                                                     | ERROR HANDLING OPTns.                                   |

|                             | 40 ( <del>//</del> 28)                                                                     | UPPER LIGHTS (DETAIL SECT.9)                            |

| : 10                        | 41 (++29)                                                                                  | LOWER LIGHTS                                            |

| Black 2-                    | 42 ( <del>//</del> 2A)                                                                     |                                                         |

|                             | 43 (#2B) Ad with to a clacked.                                                             | IPL DATA                                                |

|                             | 44 ( <del>//</del> 2C)                                                                     | OPER LIGHTS SLAVE                                       |

|                             | 45 ( <del>//</del> 2D)                                                                     | PEI PARAM                                               |

|                             | 46 ( <del>//</del> 2E)                                                                     | W.S. IDENT.                                             |

|                             | 47 (#2F)                                                                                   | SEI PARAM.                                              |

| 1900<br>Bilulatii.<br>Caly- | 64((◆40) - 71(=47) 72 (◆48) 73 (◆49) 74 (◆4A) 75 (◆4B) 76 (◆4C) 77 (◆4D) 78 (◆4E) 79 (◆4F) | 1900 ACC's 0-7 FPACØ FPAC1 DATUM LIMIT SMO ESR MEB OBEY |

|                             | 82 (#52)                                                                                   | TGT BLK ADD                                             |

|                             | 94 (#5E)                                                                                   | LAST 7 BITS of PC,LOG POINTER                           |

|                             | 96 (#60-DF)                                                                                | PC LOG AREA                                             |

HAVING LOCGED IN TO E.M.A.S. AS NORMAL PROCEED AS FOLLOWS:

COMMAND! LTP XXXX WHERE XXXX IS THE 4 CHAR PROG. NAME.

(FOR THE FOLLOWING EXAMPLE WE SHALL ASSUME XXXX = EDA

TCSS 5.2

PLEASE SELECT UNIT FOR DEVIS: YYYY WHERE YYYY = ALPHA NUMERIC MNEMONIC

1ST

FOR DEVICE TO BE TESTED

SEE NOTE 1

YYYY USED AS DEVID

PLEASE SELECT UNIT FOR DEV1: 2222 WHERE ZZZZ = ALPH NUMBRIC MNEMONIC

FOR 2MO DEVICE TO BE TESTED

SEE NOTE 1

ZZZZ USEO AS DEV1

AND NOTE 3

PLEASE SELECT UNIT FOR DEVZ: FORGO i.e. NO FURTHER TEST DEVILES

. LOGRAM EDAR (1) LOADED SUCCESSFULLY

- TCSS/TEST PROGRAM HAVE NOW BEEN ENTERED AND

ALL STANDARD TOSO/TCSS COMMANDS, WITH THE EXCEPTION

OF BREAKIN, ARE VALID. FOR BREAKIN SER NOTE 2.

FOR LIST OF VALID COMMANDS SER TCSS TPUD

- >- LGT CAUSES TOSS TEST PROGRAM TO BE DELETER AND PROCESS TO BE LOGGED OUT

DEVICE MAGMONICS

AS T.C.SS | TEST PROGRAMS REQUIRE 4 CHAR MNEMONICS ( NIEMALLY TWO ALPHA FOLLOWS BY TWO NEMERIC CHARS) AND SOME EMAS MNEMONICS ARE ONLY THREE CHARS LONG CERTAIN GROWN RULES MUST BE OBJERVED. THESE RULES ARE AS FOLLOWS :-

I EDS MHENONICS - USE EMAS MHENONIC

IN MIT MHEMONICS - IF THE LEAST SIGNICANT DECK IS MID THEM THE CONCEPTUAL EMAS CLUSTER MNEMONIC BECOMES MC10 FOR MAD THEN MC20 ETC.

iii SLOW DEVICE MAFMONICS - WHERE THERE ARE ONLY 3 CHARS IN THE EMAS MNEMONIC THEN A LEADING & IS PLACED BEFORE THE NUMERIC CHAR i.e.

> CRØ BECOMES CRØD LPI BECOMES LPOI LP11 REMAINS LP11

## M BREAKIN

AS "CONTROL &A" IS MEANINGLESS TO EMAS BREAKIN IS ACHIEVED BY HITTING "ESCAPE" ("CONTROL, SHIFT & K" OH LIMITED SET TIT COMPATIBLE VDU'S) AND WHEN PROMPTED INT: REPLYING BI. MULTIPLE BREAKINS ARE PERMISSABLE AND WILL CAUSE INSTANT BREAKIN TO TESS WHEN THE TEST PROGRAM IS RUNNING,

3 AVAILABILITY OF DEVICES FOR TESTING

BEFORE DEVICES CAN BE ARRIVED BY TOSS FOR TESTING THEY MUST BE IN THE CORRECT SYSTEM STATE, THIS CAN BE ACHIEVED AS FOLLOWS!-

IT IS SUFFICIENT TO MOUNT A NON-STANDARD DISC (i.e. EDAR DISC) ON THE DRIVE(S) TO BE TESTED.

FOR M/T'S IT IS NECCESSARY TO TYPE THE FOLLOWING AT THE MAIN CONSOL

Y/ MXX MODE = OFF

WHERE MXX IS THE ENAS MAGNINIC FOR THE DEVICE. M. F. THIS MUST BE DONE FOR EVERY DECK IN THE CLUSTER TO BE TESTED.

FOR SLOW DEVICES IT IS NECCESSARY TO TYPE THE FOLLOWING AT THE MAIN CONSUL

> S/XXX LIMIT &

> S/ABORT XXX WHERE XXX IS THE EMAS MAEMONIC OF DEVICE TO BE TESTED

SHOULD THE DEVICE(S) NOT BE IN THE REQUIRED STATE WHEN TUSS ATTEMPTS TO ACQUIRE IT THEN THE MAIN OPERATOR CONSUL WILL BE PROMPTED AS FOLLOWS:-

"PLEASE CONFIGURE OUT XXXX"

TWO COURSES OF ACTION MAY THEN BE TAREN I THE DEVICE CAN BE MADE AVAILABLE AND THE PROMPT ANSWERED "PDN" (PROMPT BONE), T.C.S.S. WILL THE CARRY ON AS NORMAL. THE PROMPT CAN BE ANSWERED "(D" (CANT DO). AN APPROPRIATE MESSAGR WILL BE OUTPUT AT THE TERMINAL AND TISS & TEST PROC. WILL BE DELETED AND THE SESSION TERMINATED.

ne AS EMAS IS NOT BLOCK STRUCTURED RESOURCES ARE NOT

NECCESSARILY SURRENDERED AT THE END OF SESSION. THE TOSS-EMAS SUPPORT PACKACE WILL, OF LOURSE, RELINAVISH ALL DEVICES ALLOCATED TO IT AT THE END OF SESSION. THIS, HOWEVER, PRE-SUPPOSES A CLEAN EXIT FROM TOSS. A SITUATION CAN ARISE WHERE TOSS IS NOT EXITED FROM IN A TIDY MANNER R.g. IN THE EVENT OF A CRASH IN THE ENGINE. PROCESS DURING RUNNING OF TOSS TEST PROCEAM. THIS CAN LEAD TO A SITUATION WHERE ENGINE OWNS A DEVICE(S) BUT T.C.SS TEST PROCEAM CANNOT USE IT AS ANY ATTEMPT TO ALLOCATE IT FAILS AS IT IS ALREADY ALLOCATED. SHOULD TOSS TEST PROCEAM CRASH DURING RUNNING IT IS ADVISED THAT ANY ALLOCATED DEVICES ARE MANNALLY RELEASED. TO THIS END A SPECIAL COMMAND "RELEASE" HAS BEEN PROVIDED. THIS TAKES THE FORM

Commann: RELEASE XXXX where XXXX IS THE EMAS MNEMBHIC

IT IS FURTHER ABVISED THAT IN THE EVENT OF A CRASH NO ATTEMPT IS MADE TO RE-ENTER TOSS WITHOUT FIRST LOGING OUT AND LOGING IN AGAIN. IT WON'T WORK AS CERTAIN TOSS VARIABLES WILL NOT HAVE BEEN RE-INITIALISED.

Document CED: 2900 - 25 - 0002

Issue: 1

Part D Sheet 1.1.

#### GENERAL DESCRIPTION SRU

#### PART 'D' SECTION 1

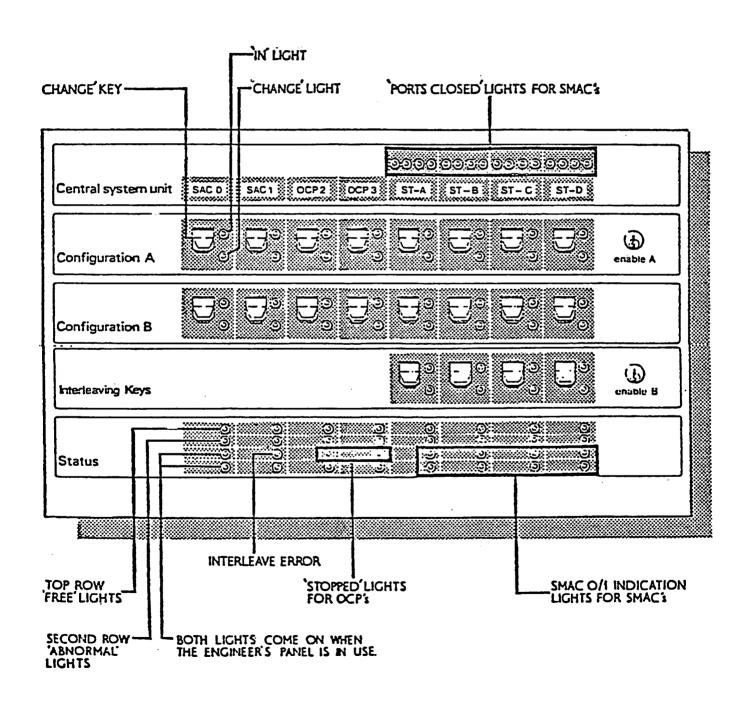

1.1 Major system units SMAC, SAC and OCP on a dual system are configured by the (SYSTEM RECONFIGURATION UNIT) SRU. System units SAC and OCP are visible to the system via the ports of SMAC. The SRU uses HI HO control over transmitters and receivers of the port interfaces, and also to isolate the (DIRECT WIRED INTERFACE) DWI. The DWI is an interface between SAC and OCP, OCP and OCP, in a dual configuration.

The configuration is set on the SRU at load time. Thereafter, the configuration is set by writing to an image store in SMAC to enable dynamic reconfiguration. This software can be envoked by the command (CONFIGURE DEVICE STATUS) CDS or by a software decision to remove a unit from the configuration if not being used.

## 1.2 The SRU

This unit has two main panels accessible to the operator. panels are divided into two. The left hand panel is the reconfiguration panel. This panel has sixteen switches, eight in either half. The 2976 has an extra 4 switches, set below the standard sixteen These are for interleaving configuration. A dual configuration can be set in either half 'A' or 'B'. If a configuration is set in both 'A' and 'B', the system is said to be partitioned. In a dual configuration all units are set in one half. To set a configuration, all switches must be put down to the change position, this will illuminate the red change light below the switch. A change can only take place if the unit is in the free state, this is indicated by a green light at the bottom of the panel. A unit is set into a configuration by the operation of the appropriate enable key 'A' or 'B'. All keys selected to the change state must be put to the normal position (up), because if the enable key for that configuration is pressed again with the key in the change position, it will be removed from the system and become free.

Other indicators on this panel are port closed lights which are positioned above the SMAC switches. These indicate when SMAC ports are closed. Along the bottom of the panel there are four rows of indicator lights. The top row of these indicate when the unit directly above it is in a 'free' state i.e. not in either configuration. The second row indicate an abnormal condition on the unit, this can be a power supply fail or an engineers switch left in an operative state. The third and fourth rows are not symmetrical and therefore will be described individually. The two lights at the left hand end indicate when lit that the engineers panel is connected to the SRU.

Part D Sheet 1.2.

2976 RECONFIGURATION PANEL

Document CED: 2900 - 25 - 0002 Issue: 1

Part D Sheet 1.3.

2976/80 BOOTSTRAP PANEL

Issue: 1

Part D Sheet 1.4.

The operation of the engineers panel will be dealt with in a separate section. The next indicator on the third row is only fitted to 2976 SRUs and indicates an interleaving error. This condition will occur when the interleaving rules are broken. The next set of lights are in the third row below the OCP change switches and indicate when the OCP is in the stopped state. The last set of lights are a group of four and relate to the SMAC number. The 2976 differs in this respect to all other 2900's the SMAC number here is always in pairs module 8 apart.

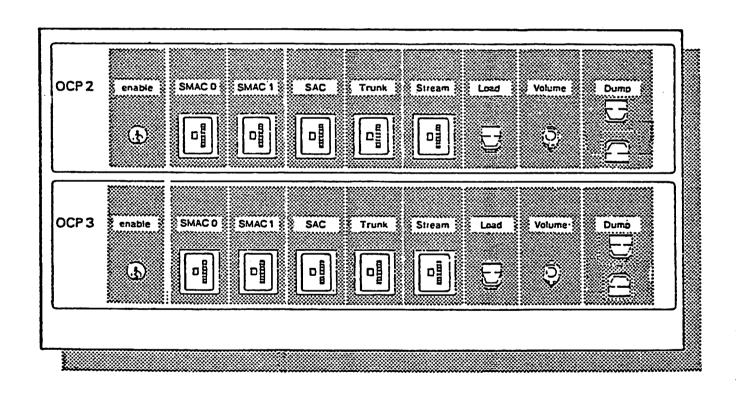

## 1.3 Bootstrap Panels

The bootstrap panels are situated on the right hand side of the SRU. These two panels are divided in two halves - one for OCP2, the other for OCP3. Each half contains thumb wheels to select the IPL path, a volume control and switches for load and dump. The panels vary in layout within the 2900 range. 2980 and 2976 have an extra thumb wheel switch, as these machines have the facility to interleave.

The operation of this panel is reasonably self-evident. The SMAC or SMAC's and SAC numbers are selected on the thumbwheels the SMAC number is in the range A to D. This letter relates to the ST letter selected on the reconfiguration panel. The letter selected will deem that SMAC to be SMAC Ø. The SAC number is in the range O to 1 as only two SAC are allowed on the system. The other two thumb wheels select the trunk and stream of the IPL path, both in the range O to F. When the selection is complete, the load or dump keys are operated simultaneously with the enable key. Note there are two dump keys for each panel which must be operated at the same time to envoke the dump sequence.

## 1.4 Engineers Panel

This panel is situated at the rear of the SRU behind the rear cover. Normally the connecting cables 1R and 2R will not be connected. As stated in section 1.2, when this connection is made a two-light display will illuminate on the operators reconfiguration panel. The purpose of the engineers switch panel is if the power supply fails in the SRU, a configuration can be set on the engineers switches to simulate the original configuration to enable the customer to continue.

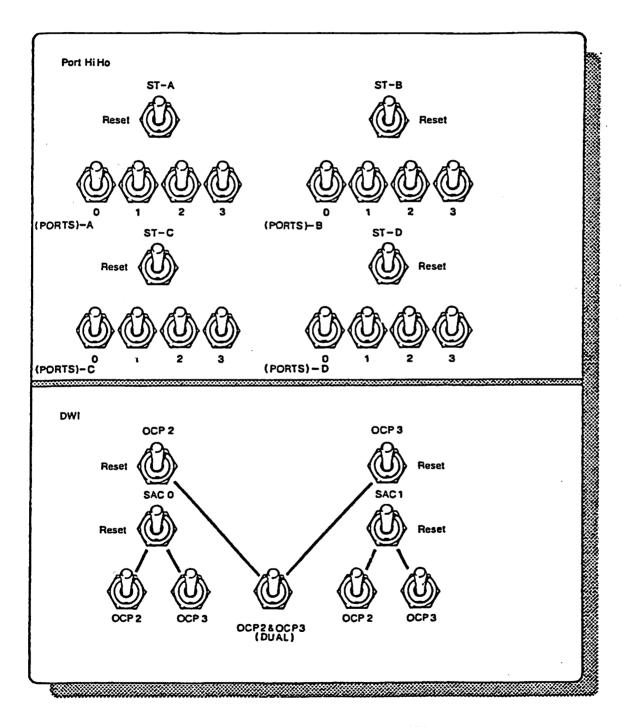

## 1.5 Engineers Panel Operation

The switches on this panel are operative when in the (up) position. There are twenty one toggle switches and eight bias switches. The panel is divided into two halves, the upper half is port control, the lower is DWI control. To set a dual configuration using two SMACs, two SACs and two OCPs, put all toggle switches 0, 1, 2, 3 up on port 'A' and 'B'. Put the lower five toggle switches up. Operate the bias switches for port 'A' and 'B'. Operate the bias switches on the DWI half for OCP2, OCP3, SAC Ø and SAC1. The bias switches produce local IPL signals and open the path for the IPL. Complete system load as per section 2.4, 3.4 4.7 for 2960, 2970 and 2976 respectively.

Document CED: 2900 - 25 - 0002 Issue: 1

Part D Sheet 1.5.

ENGINEERS PANEL

NOTE: THE POSITION OF THE KEYS SHOWN IN THIS FIGURE IS THE "OPERATIVE" POSITION

Document CED: 2900 - 25 - 0002 Issue: 1

Part D Sheet 1.6.

To partition neatly in two balanced halves using one SMAC in each half, set the switches as follows: