Scanned from a physical document (donated by a kind former ICL employee)

Number

6594899

Sheet Issue

THIS DOCUMENT IS COMPANY RESTRICTED

| Issue     | 1      |   |  |

|-----------|--------|---|--|

| Des. Auth | 000    |   |  |

| CED       | KE. 12 |   |  |

| Tech.Lit. | 9260   | 1 |  |

Issue

The policy of International Computers Limited is one of continuous development and improvement of its products and services, and the right is therefore reserved to alter the information contained in this document without notice. ICL makes every endeavour to ensure the accuracy of the contents of this document but does not accept liability for any error or omission. Any equipment or software performance figures and times stated herein are those which ICL expects to be achieved in normal circumstances. Wherever practicable, ICL is willing to verify upon request the accuracy of any specific matter contained in this document.

Issued by Technical Literature Department, International Computers Limited, Wenlock Way, West Gorton, Manchester. M12 5DR.

Printed by Reprographic Services, West Gorton, Manchester.

Number Sheet Issue 6594899 3

1

## CONTENTS

| Section |                                  | Sheets       |

|---------|----------------------------------|--------------|

| 1 .     | INSTRUCTION FORMATS              | . 1.1 - 1.25 |

| 2       | DESCRIPTOR FORMATS               | 2.1 - 2.5    |

| 3       | OPERAND ADDRESSING AND ALIGNMENT | 3.1 - 3.6    |

| 4       | STACK INSTRUCTIONS               | 4.1 - 4.10   |

| 5       | ACCUMULATOR INSTRUCTIONS         | 5.1 - 5.9    |

| 6       | CONTROL AND JUMP INSTRUCTIONS    | 6.1 - 6.15   |

| 7       | B INSTRUCTIONS                   | 7.1 - 7.11   |

| 8       | DR INSTRUCTIONS                  | 8.1 - 8.15   |

| 9       | COMPUTATIONAL FUNCTIONS          | 9.1 - 9.44   |

| 10      | STORE TO STORE FUNCTIONS         | 10.1 - 10.31 |

| 11      | MISCELLANEOUS FUNCTIONS          | 11.1 - 11.10 |

| 12      | PROGRAM ERRORS                   | 12 1 - 12 6  |

### APPENDICES

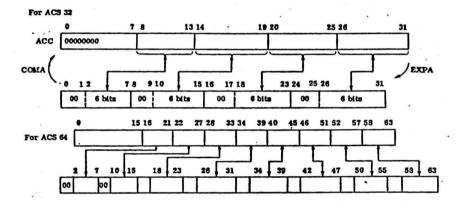

| Appendix |                                                     | Sheets      |

|----------|-----------------------------------------------------|-------------|

| 1        | LIST OF INSTRUCTIONS IN MNEMONIC ALPHABETICAL ORDER | Al.1 - Al.4 |

| 2        | FUNCTIONAL GROUPING OF 2900 ORDERS                  | A2.1 - A2.7 |

### Related Documents

6594801 - 2900 Architecture.

#### 1. INSTRUCTION FORMATS.

### 1.1' Hexadecimal Notation.

2900 is based on the use of the 8-bit byte, each byte consisting of two 4-bit groups which are hexadecimal in character, i.e. they are capable of holding the range of values 0-15. Hexadecimal values are denoted by a preceding # character, thus #9A denotes the binary equivalent 10011010, and, as a further example, #FC is equivalent to the binary value, 111111100.

The following table shows the hexadecimal scale together with binary and decimal equivalents:

| Hexadecimal | Binary | Decimal |

|-------------|--------|---------|

| # 0         | 0000   | 0       |

| # 1         | 0001   | 1       |

| #2          | 0010   | 2       |

| #3          | 0011   | 3       |

| #4          | 0100   | 4       |

| #5          | 0101   | 5       |

| #6          | 0110   | 6       |

| #7          | 0111   | 7       |

| #8          | 1000   | 8       |

| #9          | 1001   | 9.      |

| #A          | 1010   | 10      |

| # B         | 1011   | 11      |

| #C          | 1100   | 12      |

| #D          | 1101   | 13      |

| #E          | 1110   | 14      |

| #F          | 1111   | 15      |

|             |        |         |

All diagrams are shown with the store Least Significant Word at the top of the diagram (this includes the diagrams showing the stack).

Number 6594899 Sheet 1.2 Issue 1

### 1.2 Architectural Mod. Levels

The concept of Architectural Mod'Levels (AML) is introduced to allow for progressive enhancement to the primitive level interface without instantaneously impacting the total population of 2900 systems.

The basic AML is AML0 and it is a rule that AMLs are forwards compatible such that software written for system at AML0 will run on systems at AML1.

The AML of systems can be read from line 16 of Block 0 of the Image Store.

#### 1.2.1 Summary of Additional Facilities at AML1.

#### Facility

- 1. Additional format for RRTC

- 2. Alternative form of VALIDATE instruction

- 3. System Call count

- 4. Parameter space check for System Calls

- 5. Addition of bit string operand form

- 6. Addition of TEST, CLEAR and SET instructions

- 7. (B + N) Operand form

- 8. Vector Descriptor, type 0, size code 4 ( ≡ 16 bits)

- 9. Vector descriptor, for signed items.

### 1.3 Instruction Lengths

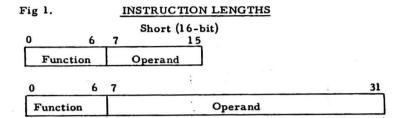

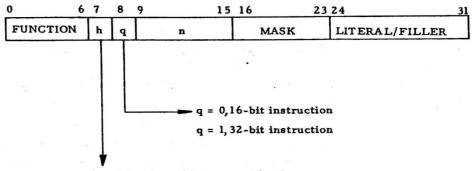

2900 makes a use of two distinct instruction lengths, i.e. short (16-bit) or long (32-bit). In either case the function occupies bits 0-6, the operand occupying either bits 7-15 or 7-31 according to instruction length. (Fig 1).

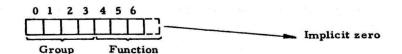

#### 1.4 Function Decode

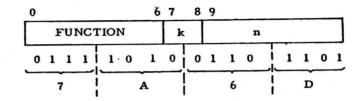

From fig 2 it can be seen that the function code bits 0-6 are regarded as two hexadecimal characters, the L.S. bit of the second character being implied zero. The first character denotes the order code group, the second denotes the function number within the group. The order code thus contains 16 groups, each group containing up to 8 functions (since only even-numbered function values can be specified). The function codes # 00 and #FE are illegal. There are therefore 126 permissible function codes ranging from # 02 to #FC, some of these being as yet unassigned.

Fig 2. FUNCTION DECODE

### 1.5 Instruction Types

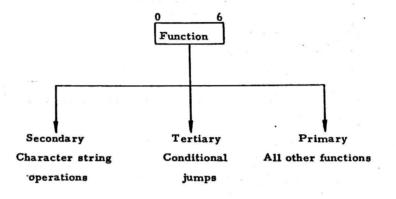

There are three distinct instruction types, primary, secondary and tertiary (fig 3), each requiring a different operand field format.

Fig 3 <u>INSTRUCTION TYPES</u>

Primary instructions use the operand field solely to specify either an address or a literal value. Secondary instructions are concerned with character string manipulation and thus require to use the operand field for specification of values such as a string length, byte mask, byte filler character etc.

The tertiary instructions are all conditional jumps and thus have to specify a jump address and also the jump condition. Identification of the instruction type determines the method of interpreting and decoding the operand field. The instruction type is recognised from the function bit decode as indicated in fig 2.

### 1.6 Operand Format of Primary Functions

Functions are provided which perform numerous operations on the special addressing registers, i.e. LNB, CTB, XNB, DR, SF and the central computational registers i.e. the accumulator ACC and the indexing register, B. A simplified summary of the available functions is shown in fig 4 below.

- Load LNB, store LNB, raise LNB, load XNB, store XNB, adjust SF, load CTB, store CTB.

- Simple jump functions (unconditional jumps), jump and link, decrement B and jump.

- Functions used to jump into and return from procedures,

i.e. call. exit. escape-exit.

- 4. Semaphore instructions; increment and test, test and decrement.

- Simple non-computational operations (load, store, stack and load), computational functions (add, multiply, etc) and boolean operations on the ACC (not equivalence, and, or).

- Operations on the index register B and the descriptor register DR.

- 7. Miscellaneous, e.g. idle, read real time clock.

#### Fig 4. PRIMARY FUNCTIONS

#### 1.7 K Decode

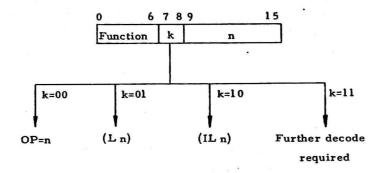

Fig 5 shows the operand field for primary instructions. Taking a 16-bit instruction, the 9-bit operand field is decoded into a 2-bit k-field and a 7-bit n-field.

Number 6594899 Sheet 1.6 Issue 1

Fig 5. FORMAT OF OPERAND FIELD (PRIMARY INSTRUCTIONS) - k DECODE

- k OPERAND

- 00 Literal n

- 01 Literal at Ln

- 10 Literal at IL n

- 11 Further Decode Required

n must be ≤ 127

If k = 00 (i. e. 0) then n is taken as a literal operand and is interpreted as a signed integer in the range:  $-64 \le n \le +63$ .

If k = 01 (i. e. 1), the operand addressing form is L n, i.e. the contents of the item at the location LNB + n. In this case, n is interpreted as an unsigned integer in the range :  $0 \le n \le 127$ .

For k = 10 (i.e. 2), the operand addressing form is IL n, i.e. indirect access to the final operand via a descriptor which is stored at the location LNB + n. Again, n is an unsigned integer in the range:  $0 \le n \le 127$ .

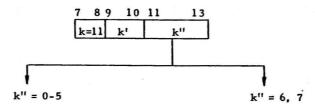

### 1.8 k = 3 decode.

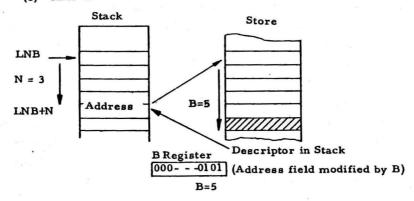

If k = 11 (i. e. 3), the hardware has to perform another decode of two further fields k' and k''. See fig 6.

32-bit Instruction

16-bit Instruction

k' defines whether access is direct or indirect, If indirect, gives information about descriptor.

k'

00 Direct access

01 Indirect access (desc. in DR modified)

10 Indirect access (desc. in store)

11 Indirect access (desc. in store modified)

Fig 6. FORMAT OF OPERAND FIELD (PRIMARY INSTRUCTIONS) - k' DECODE

The k" - field occupies bits 11-13 and indicates the register by means of which the operand is accessed. It also determines whether the instruction length is 16 or 32 bits. Note, that for a 16-bit instruction the quantity n is written as a lower-case character; for 32-bit instructions, it is specified as an upper-case character N. This, being an 18-bit field, has a greater range than n, which is, of course 7 bits long.

Sheet 1.8 Issue 1

This manual has been written in terms of SFL formats.

The table given below lists STAPLE equivalents.

#### Table 1

| SFL  |   | STAPLE           | SFL  |   | STAPLE       |

|------|---|------------------|------|---|--------------|

| "N   |   | (signed literal) | .c   | N | (CTB+N)      |

| ,D   | N | (DR+N)           | DQ.  | N | (DR+(CTB+N)) |

| ,G   |   | (IS location N)  | ,IC  | N | ((CTB+N))    |

| .GB  |   | (IS location B)  | .MIC | N | ((CTB+N)+B)  |

| .L   | N | (LNB+N)          | т.   |   | τos          |

| ,DL  | N | (DR+(LNB+N))     | .DT  |   | (DR+TOS)     |

| .IL  | N | ((LNB+N))        | .IT  |   | (TOS)        |

| .MIL | N | ((LNB+N)+B)      | .MIT |   | (TOS+B)      |

| .x   | N | (XNB+N)          | .в   |   | В            |

| .DX  | N | (DR+(XNB+N))     | .B   | N | (B+N)        |

| .IX  | N | ((XNB+N))        | a.   |   | (DR)         |

| .MIX | N | ((XNB+N)+B)      | .MD  |   | (DR+B)       |

| .Р   | N | (PC+N)           |      |   |              |

| .DP  | N | (DR+(PC+N))      | •    |   |              |

| .IP  | N | ((PC+N))         |      |   |              |

| .MIP | N | ((PC+N)+B)       |      |   |              |

An SFL instruction takes the form:

MNEM .VAR OP1, OP2, - - - OPn

where:

MNEM is the mnemonic of the instruction (1 to 5 letters)

VAR is the optional SFL variant

OP1, OP2, - - - OPn are the operands of the instruction.

Issue 1

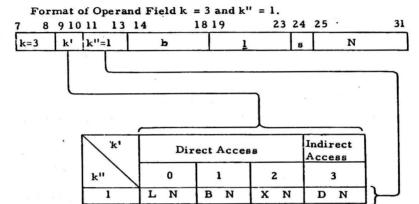

| 7 8 9 10 11 12 13 14 15 7 8 9 10 11 12 13 14 31 k k' k" N (11) |    |         |     |                             |        |                       |       |         |      | <u>ן</u><br>ר |   |

|----------------------------------------------------------------|----|---------|-----|-----------------------------|--------|-----------------------|-------|---------|------|---------------|---|

|                                                                | k' | DIRECT  |     |                             |        | INDIREC               | т     |         |      | 寸             |   |

|                                                                | k" | . 0     |     | l<br>Desc. in D<br>modified |        | Desc. in              | store | Desc.   |      |               |   |

|                                                                | 0  | mn      | N   | mn .D                       | N      | * IS locati<br>mn . G |       | *IS loc |      | В             |   |

|                                                                | _1 |         | Bit | String Ha                   | ndling | (Section              | 1,12) |         |      |               | 1 |

|                                                                | 2  | mn .L   | N   | mn .DL                      |        | mn JL                 | N     | mn M    | IL N | 1             | Ų |

|                                                                | 3  | mn X    | N   | mn .DX                      | N      | mn .IX                | N     | mn .M   | 1 X  | 1             |   |

| 1                                                              | 4  | mn .P   | N   | mn DP                       | N      | mn .IP                | N     | mn . M  | IP N | 1             |   |

|                                                                | 5  | mn ,C   | N   | mn .DC                      | N      | mn . IC               | N     | mn M    | IC N | 1             |   |

| U                                                              | 6  | mn .T . |     | mn .DT                      |        | mn IT                 |       | mn .M   | IT   |               |   |

|                                                                | 7  | mn .B   |     | mn ,B                       | N*+    | mn .D                 |       | mn .N   | (D   |               |   |

- i. PC contains address of current instruction.

- ii. MIX N, MIT, MD indicate items pointed to by descriptors held in XNB+N, top 2 words of stack, and in DR respectively The 'M' indicates that the address in each descriptor is to be modified by B.

- iii. Operand format for k" = 1 is as follows

AML0 Unassigned

AML1 given in section 1.12

- vi. The equivalent STAPLE operand formats are in Table 1.

- \*Classed as direct address form.

- +32 bit format. The format was unassigned at AMLO and is still provisional.

Fig. 7. FORMAT OF OPERAND FIELD (PRIMARY

INSTRUCTIONS) - k" DECODE

Number 6594899 Sheet 1.10 Issue 1

### 1.9 Direct Access Decode - k' = 0

Figure 7 shows the instruction formats in greater detail. Taking a value of k' = 0, i. e. direct access, let us examine the possible values of k''.

<u>k" = 0</u> indicates that the operand is, in fact, the literal N, i.e. bits 14-31 of the instruction. N is a signed quantity in the range:  $-27^{17} < n < 2^{17}-1$

k" = 1 Bit string handling (See section 1.12)

### k" = 2-4 Decode

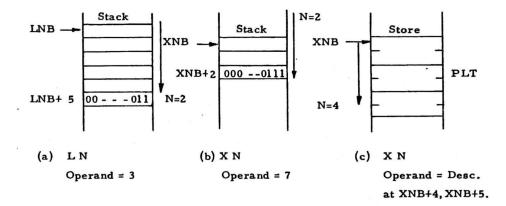

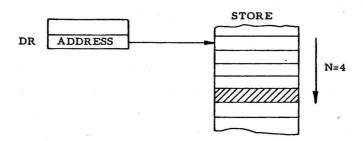

k" = 2 uses L N, i.e. the contents of the location LNB+N, as the operand. See fig 8 (a). LNB points, as always to a location within the stack. In our case N = 5, so the fifth item above LNB is accessed. The contents of that location are 3, so the operand used is 3. Note that here N is an unsigned (positive) quantity and access below LNB, (i.e. LNB-N) is not possible.

k'' = 3 uses (X N) i.e. the contents of the location XNB+N, as the operand. In the example shown in fig 8 (b), N = 2 thus operand = 7. XNB is a hardware register which can point anywhere within the store. In fig 8 (b). XNB points to a location within the stack.

If XNB points at, say a table of descriptors in store, then operand access is as shown in fig 8 (c). The quantity N is a word count, so the operand form (XNB + 4) will, in fact, access the third descriptor in the table, i.e. the one at XNB + 4 and XNB + 5. A typical use for this operand form would be to load a descriptor into DR.

$\underline{k''=4}$  accesses P N, i.e. the contents of the item at PC+N are used. PC is the Program Counter, which contains the address of the current instruction, Here, N is a signed quantity.

Number 6594899 Sheet 1.11 Issue 1

Fig. 8 PRIMARY FUNCTIONS - DIRECT OPERAND ACCESS

Fig. 9 DIRECT OPERAND ACCESS

Number 6594899 Sheet 1.12 Issue 1

#### k" = 5-7 Decode

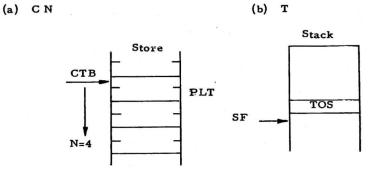

k" = 5 uses C N (the contents of location CTB+N) as the operand CTB is a hardware register that may point anywhere in store.

Thus, CTB is used in a similar way to XNB. CTB will usually be used to point to a PLT (Procedure Linkage Table) in Store. Fig. 9

(a) shows the operand (C+4) accessing the third descriptor in the PLT.

k" = 6 uses T (TOS). This points to the item to be read from the stack in the case of a read instruction (Load ACC for example). If a 4-word item is expected at TOS and it is really only two words long then, on a TOS access, a 4-word item will be picked up.

Conversely, if a single word item is expected at TOS and it is 2 words long, a truncated item will be accessed giving incorrect results. (When writing programs it is important to keep track of the size of stacked items).

When using this operand format with an instruction which writes the operand away, the item is written to TOS + 1, in the case of a single word item, or to TOS + 1, TOS + 2 in the case of a double word item, etc., SF points to this next available location on the stack and will be incremented or decremented by the size of the item added or taken from the top of stack. See fig. 9 (b).

k'' = 7 Here the actual contents of the B register will be used.

That covers k' = 0 which is DIRECT ACCESS.

In all the accesses shown in fig. 7, N is an unsigned positive quantity except when it is a literal, or when added to PC.

### 1.10 Indirect Access Decode

k' = 1, 2 and 3 all indicate indirect access format.

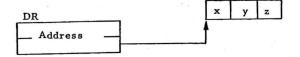

1.10.1 k' = 1 This indicates indirect access via a descriptor in DR.

k'' = 0 Fig. 10 (a) shows DR pointing to a location in store. The address of the location is modified by the literal N and the item thus

accessed is the operand.

k" = 1 Bit string handling (see 1.12)

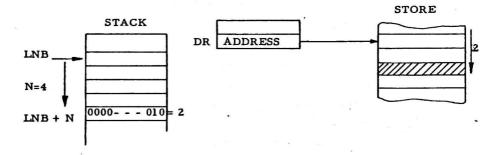

k" = 2 Here the address in DR is modified by the contents of the location LNB+N. Fig. 10 (b) uses N = 4, the contents of LNB+4 are 2, so the operand is to be found in the location pointed to by the address in DR modified by two.

Similarly for k'' = 3, 4 and 5 the address in DR is modified by (XNB+N), (PC+N) and (CTB+N) respectively to access the operand. For k'' = 6 the address in DR is modified by the item at the top of stack.

k'' = 7 Contents of B modified by N, is used as the <u>operand</u> (the exception case).

1.10.2  $\underline{k' = 2}$  Moving on to k' = 2, this deals with indirect access via a descriptor in store.

We'll ignore k'' = 0 for now and come back to it later (section 1.11). k'' = 1 See section 1.12.

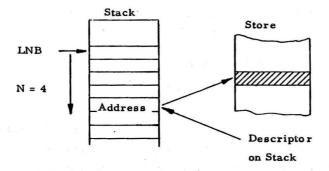

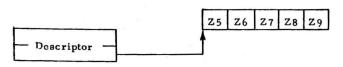

<u>k" = 2</u> Fig. 11 (a) shows a descriptor occupying the locations LNB+4, LNB+5 on the stack. The address field of the descriptor points to an item in store, which is used as the operand.

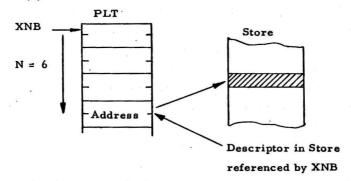

k" = 3 If XNB points within the stack, then the operand access is similar to that for IL N. However, if XNB points at say a PLT then the operand access is as shown in fig. 11 (b). N, which is a word address, is added to the address of the start of the PLT and the relevant descriptor is accessed. In the diagram N=6, so the fourth descriptor which is at XNB+6 and XNB+7 is accessed. The address field of this descriptor points at the operand.

Issue 1

Fig. 10. INDIRECT OPERAND ACCESS via Descriptor in DR

# (b) DL N

Number 6594899 Sheet 1.15 Issue 1

Fig. 11 - INDIRECT OPERAND ACCESS VIA A DESCRIPTOR

# (a) IL N

### (b) IX N

# (c) MIL N

k'' = 4, 5. There is a descriptor in store at PC + N and CTB + N, respectively, and it is the address field which points at the operand to be used.

k'' = 6, 7. Indicate that the descriptors at TOS and in DR, respectively point at the operand.

1.10.3 k' = 3 deals with INDIRECT ACCESS via a descriptor in store. We'll tackle k'' = 0 later (section 1.11)

k'' = 1 see section 1.12

$\underline{k''} = 2$ . There is a descriptor on the stack at LNB + N and LNB + N + 1

The address field points to an area in store. The address of this area is modified by the contents of the index register, B to give the operand required. See fig 11 (c).

k'' = 3, 4, 5. Similarly the addresses of the descriptors at (i) XNB+N and XNB+N+1, (ii) PC + N and PC + N + 1, (iii) CTB + N and CTB+N+1, respectively are modified by the contents of the B register to access the operand.

$\underline{k''}$  = 6, 7. Indicates that there is a descriptor at TOS or in DR, respectively. The address field is modified by B to give the operand required.

1.11 Image Store Formats (k" = 0 for k! = 2 and 3)

These primary formats are I. S. location N and I. S. location B - these are the IMAGE STORE formats. The image store mechanism is a method of addressing hardware registers in the system. It provides a method of performing operations at a hardware level, which for reasons of privilege, timing or level of control could not be performed at a software level, it is the image store mechanism which is used to kick off peripheral transfers. Two options of image store addressing i.e. I. S. location N and I. S. location B are offered. The former allows addressing up to  $2^{18}$  - 1, since N is an 18 bit literal (extended with zeros on the left). The latter allows addressing up to  $2^{32}$  - 1, since the contents of the B register are used.

Number 6594899 Sheet 1.17 Issue 1

#### 1.12 Bit String Handling

Facilities for bit string handling are available in machines at AML 1.

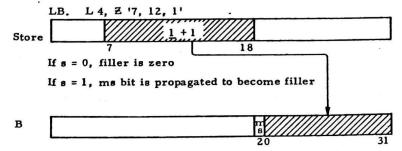

NOTE:- In this section the lower case letter L is shown as  $\underline{1}$  to differentiate it from 1 (the number one).

Where:

b and 1 define a bit string within a 32 bit word

b = number of most significant bit of the string

1 = one less than the number of bits in the string.

(e.g. b = 7, 1 = 11, defines a 12 bit string occupying bits 7 to 18 inclusive of the 32 bit word.

For indirect access, the descriptor in DR must be a word vector descriptor type 0, size 5 (32 bits) and

The effect of the operand depends upon the instruction as follows:

must be scaled i.e. USC not set.

(a) Operand fetch: The contents of the bit string location become the least significant 1 + 1 bits of the operand. The other bits of the operand are set as follows:

if s = 0, the filler is zero

if s = 1, the filler is the most significant bit of the bit string.

Number 6594899 Sheet 1.18 Issue 1

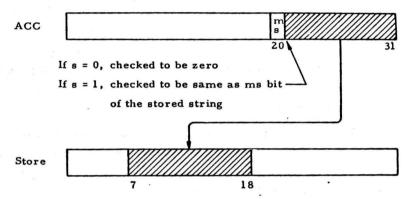

(b) Operand store: The least significant <u>1</u> + 1 bits of the operand are stored in the bit string location.

if s = 0, the remainder of the operand is checked to be all zero.

if s = 1, the remainder of the operand is checked to be the same

as the most significant bit of the stored bit string.

Note that the 32 bit word containing the bit string is written to store without hardware interlocks to prevent access from other units in the system, (except as defined for particular functions - INCT, TDEC)

There will be a program error interrupt if:

- (i) bit string operand is accessed via (DR + N) and descriptor in DR is not type 0, size 32 bits, USC unset.

- (ii) bit string operand has  $b + \underline{1} > 31$  i.e. the bit string does not lie within a 32 bit word.

- (iii) truncated part of operand not all zeros or all ones as defined in (b) above.

- 1.12.1 Functions Prohibited with this format.

Bit string operands are prohibited for the following functions

- (i) J, JLK, CALL and DEBJ

- (ii) Functions which require literal operandsi.e. ESEX, IDLE, PRCL, RRTC, CDEC and CBIN.

- 1.12.2 Example 1: Load B from the location indicated by LNB4.

The instruction in SFL would be:

Issue 1

Example 2: Store contents of ACC

The instruction in SFL would be:

ST. L4, Z '7, 12, 1'

Example 3: Clear bits 7 to 18 (inclusive) of a word located at LNB+4.

The instruction in SFL would be:

CLR. L4, Z '7, 12, 0' ..

Here

$$k=3$$

$b=7$  the first bit number  $k'=0$   $k''=1$   $\underline{1}=11$  which is one less than the number of bits in the string

Example 4: Test bits 1 and 2 of the word FRED

s = 0

The instruction in SFL would be:

TEST, FRED, Z '1, 2, 0'

Issue 1

## 1.13 Operand Format of Secondary Functions

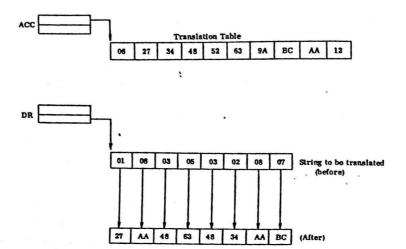

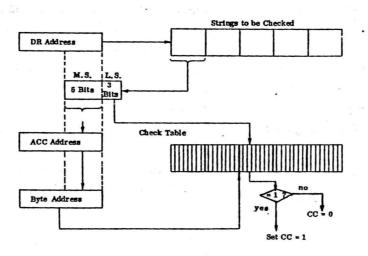

There are 16 possible functions in this group, not all of which have been allocated. They are included in the instruction repertoire specifically to assist commercial data processing establishments, where the handling of variable length data items is of paramount importance. All of these instructions are store-to-store functions. The range of instructions is quite comprehensive and it is possible to perform the following types of operations:-

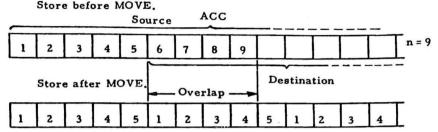

- Move a string of bytes from one part of store (referred to as

the SOURCE) to another part of the store (known as the

DESTINATION), carrying out editing or translating during the

transfers.

- Checking to determine if a pair of strings of bytes overlap in store.

- Scan a string of bytes, searching for equality with a specified byte pattern.

- 4. Boolean operations between strings.

- Scan a string of bytes, checking a table of check bits.

Translate the contents of a string of bytes, according to a table of bytes, called a 'translate table'.

- 6. Pack and unpack decimal data.

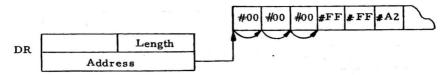

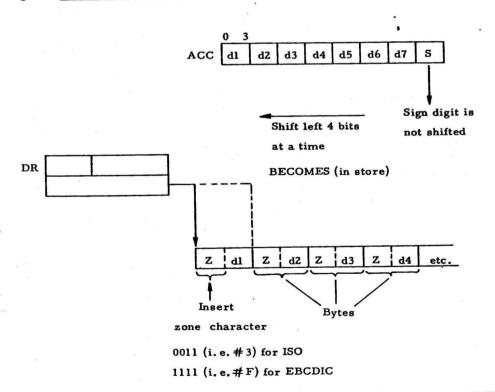

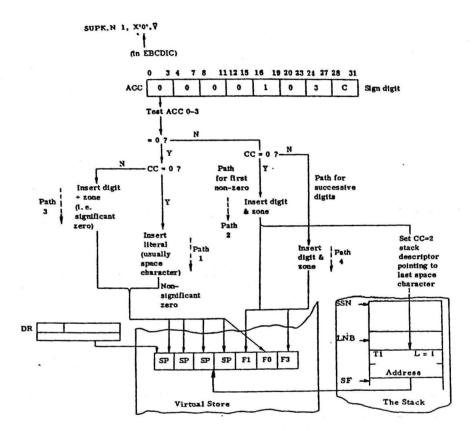

Fig 12 SECONDARY FUNCTIONS (STORE-TO-STORE OPERATIONS)

h = 0, Number of bytes = n + 1 = L

h = 1, Number of bytes = length of destination string = L

Number of Bytes involved in a Store-to-Store Operation is referred to as L.

The secondary functions may be divided into the following 3 classes:-

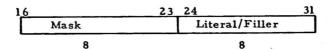

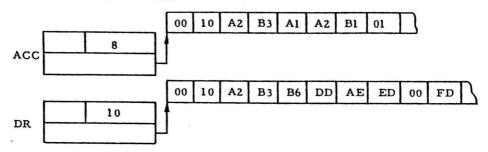

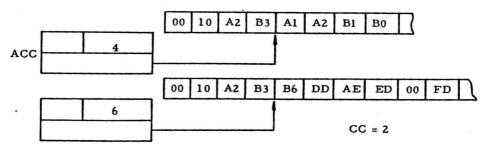

Class 1 These operations take place between two byte strings.

The SOURCE string is usually specified by a string descriptor held in the ACCUMULATOR - hence this can be referred to as the (ACC) string - and the DESTINATION string is normally specified by another descriptor, held in DR - generally referred to as the (DR) string.

Issue 1

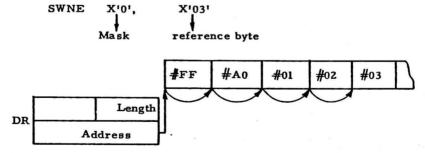

Class 2 ACC is not involved in this class. The source string consists of a series of copies of a single byte - also called REFERENCE byte. In the case of the 16-bit instructions, the byte is obtained from the index register B. In the 32-bit format, the byte is normally obtained from the field which contains the literal filler byte.

Class 3 For these functions, the (DR) string interacts directly with the contents of the ACC itself.

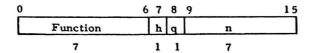

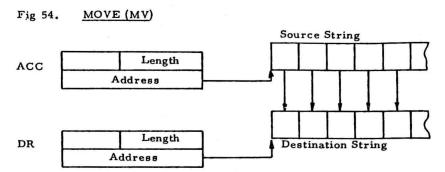

The format of secondary instructions is shown in figure 12. Bits 0-6 contain the function field, bit 7 is the h-field, bit 8 is the q-field and bits 9-15 contain the n-field. For a 32-bit instruction, bits 16-23 contain the MASK byte and bits 24-31 the LITERAL/FILLER byte.

Taking the <u>h-field</u> first - this defines how the number of bytes(L) involved in a store-to-store operation is to be specified. If h=0 then L is defined explicitly as L=n+1 where n is an unsigned integer in the range 0 < n < 127. Of course, the n-field referred to, is the one in bits 9-15 of the instruction. The alternative way of defining L is implicitly, as the length field of the (DR) descriptor where L is in the range  $0 < L < 2^{24}$ . Here h=1 and the n-field of the instruction is classed as reserved. The q-field indicates the length of the instruction: q=0 is used for a 16-bit instruction. The significance of the mask and literal/filler bytes will be explained in detail in Chapter 10 which deals with store-to-store functions.

### 1.14 Operand Format of Tertiary Functions

Only three functions of this type have so far been assigned - See fig. 13. They are all jumps and have the mnemonic codes JAT (jump on arithmetic true), JAF (jump on arithmetic false) and JCC (jump on condition code) - they will be described in detail in Chapter 6. The format of the operand field is also shown in fig 13. Bits 0-6 contain the function, bits 7-10 the MASK field and bits 11-13 the k''' field. For a 16-bit instruction, bits 14 and 15 are both zero, but for 32-bit instructions, bits 14-31 represent N.

### Fig 13 TERTIARY FUNCTIONS

JAT Jump on Arithmetic (Condition) True

JAF Jump on Arithmetic (Condition) False

JCC Jump on Condition Code

## TERTIARY GROUP FORMATS

| 0 6      | 7 10 | 10 11 12 13 14 15 16 |   |   |  |  |  |  |

|----------|------|----------------------|---|---|--|--|--|--|

| FUNCTION | MASK | k"'                  | N | N |  |  |  |  |

| k'" | OPERAND |

|-----|---------|

| 000 | N       |

| 001 | D N     |

| 010 | LN      |

| 011 | X N     |

| 100 | PN      |

| 101 | CN      |

| 110 | D       |

| 111 | MD      |

32 Bit Instruction

16 Bit Instruction

NOTE For 16-bit instruction, bits 14, 15 = 0

For 32-bit instruction, N = bits 14-31

The k''' - field provides for 8 different operand types. Note that for k''' = 0 or 4 the contents of the N-field are interpreted as a signed integer, in all other cases N is an unsigned integer. When k''' = 0, the contents of the N-field are treated as a number of half-words and are added to the current contents of the control register PC. In this case we have a relative jump. An interrupt will occur if the addition alters the segment number part of PC. Note that k''' = 6, 7 implies a 16-bit instruction.

### 1.15 Function Mnemonics

When writing programs in SFL, the mnemonic form of an instruction can be used rather than its hexadecimal representation. See fig 14.

Thus if we wish to load the B register with a value of -19, the hexadecimal representation of the instruction would be #7A6D.

However, it is perfectly in order to write LB -19.

When the program is compiled the mnemonic form will be translated into the hexadecimal equivalent, which will be understood by the machine.

This mnemonic facility is useful since a program can be written more easily and far more quickly this way than by working out the hexadecimal pattern. Also it is much less prone to errors - once the compiler has been tested and is working it will always decode the mnemonics correctly, which is more than can be said for each programmer doing it individually.

Figure 14 shows three examples of the use of mnemonics in writing programs, and illustrates (in hexadecimal representation) how it would appear in store.

### Fig 14 FUNCTION MNEMONICS

Format: function mnemonic operand

Example 1 LB -19 loads B register with -19

This is a Primary Instruction, therefore the Primary format is used, as shown in figure 5

function # 7A = LB

operand n = -19 = 1101101 (binary)

k = 00

Thus hex equivalent of LB -19 is # 7A6D:

- Example 2 LB L8 loads B register with the contents of location LNB+8. (k=01) The hex. pattern is 0111/1010/1000/1000 (i.e. # 7A88).

- Example 3 LB IL 5 accesses descriptor in LNB+5,

LNB+6. The address field points to an item

in Store. This item is loaded into B. The

hex. pattern is 0111/1010/0000/0101 (ie

# 7A05). (k=10)

Number 6594899 Sheet 2.1 Issue 1

## DESCRIPTOR FORMATS

All descriptors are 64 bits in length. The less significant 32 bits always contain a byte address, which may be modified in the course of accessing the information to which the descriptor refers.

The resultant address points to the left most (lowest addressed) byte of the information.

Descriptor types are distinguished by their more significant 32 bits.

The different types, and interpretations of the fields are as follows:-

Type 0 - Vector Descriptors

| . 0   | ) | - 1 | 2    | 4 | 5 | 6   | 7    | 8 |              | 31 |

|-------|---|-----|------|---|---|-----|------|---|--------------|----|

| m.s   | 0 | 0   | SIZE |   | S | USC | BCI  |   | Bound/Length |    |

| 1. s. |   |     | -    | • |   | •   | Byte | A | ddress       |    |

Type 1 - String Descriptors

| *     | 0        | 1 | 2 |   |   |   |   | 7 | 8  |            | 31 |

|-------|----------|---|---|---|---|---|---|---|----|------------|----|

| m.s   | 0        | 1 | 0 | 1 | 1 | 0 | 0 | Ō |    | Length     |    |

| 1. s. | $\vdash$ |   |   |   | - |   |   |   | By | te Address |    |

#### Type 2 - Descriptor Descriptor

As for type 0 except bits 0, 1 = 10 and only size 64 allowed.

### Type 3 - Miscellaneous Descriptors

#### Bits 2-7 define a subtype number

#### Subtype

- 32 bounded code, first byte = 'E0'

- 33 Unbounded code, first byte = 'El'

- 34 System Call, first byte = 'E3'

- 37 Escape, first byte = 'E5'

- 40 Semaphore (bounded), first byte = 'E8'

- 41 Semaphore (unbounded), first byte = 'E9'

- 63 Null, first byte = 'FF'

## FIG 15 DESCRIPTOR FORMATS

Number 6594899 Sheet 2.2 Issue 1

## 2.1 Type 0 = Vector Descriptors (fig. 15)

Size The size of the addressed item in store. Permitted sizes, and the corresponding size codes, are as follows:-

| Size (bits) | Code |  |  |

|-------------|------|--|--|

| 1           | 0    |  |  |

| 8           | 3    |  |  |

| 16          | 4    |  |  |

| 32          | 5    |  |  |

| 64          | 6    |  |  |

| 128         | 7    |  |  |

When the size is 32, 64 or 128 bits, the two least significant bits of the byte address, after modification, if any, are ignored - i.e. 1-, 2-, and 4- word items are made to start on word boundaries. Use of other values will cause program errors as indicated in Chapter 12. When the size is 16 bits, the 1.s. bit of the byte address after modification is ignored. Size code 4 is not available at AMLO.

- S Signed. If set to 1, then

- a) if the operand is read from Store and the addressed item is smaller than the operand length, it is sign-extended.

- b) if the operand is written to Store and the addressed item is greater than the operand length, the truncated bits are checked to be equal to the most significant bit of the stored item.

The S field is ignored at AMLO.

USC Unscaled. Unless this bit is a 1, when a modifier is added to the address field it is scaled according to the size field; 1, 2, 3 and 4 places up for 16, 32, 64 and 128 bits, respectively, and 3 places down (logically) for 1 bit. In the latter case the least significant 3 bits of the shifted-down modifier specify the individual bit number (0 = most significant) which is to be accessed within the addressed byte. If the modifier is unscaled the accessed bit-number is undefined: however if the descriptor is unmodified, bit 0 is accessed.

BCI Bound Check Inhibit. Unless this bit is 1 any modifier added to the address is checked (before scaling) to ensure that it is less than the contents of the Bound field; in this case bits 0-7 of the 32-bit modifier must be all zeros.

Bound/ The contents of this field are unsigned (positive). Length

When a byte-vector descriptor, i.e. one with Type = 0, Size code = 3, is used as the operand of a store to store instruction, this field contains the length of the byte string. On other occasions when vector descriptors with any permitted size code are used, this field is spare if BCI = 1; if BCI = 0 its contents should be 1 greater than the largest permitted modifier.

## 2.2 Type 1 = String Descriptors (fig. 15)

Size Should be set to 011 - this is checked by store-to-store instructions; at any other times it is ignored (reserved).

S This bit is reserved for use within the I/O sub-system and is ignored by the OCP.

USC These fields are ignored (reserved) and should be set to BCI 00. Modifications are not scaled or checked.

Length The length field contains the length, in bytes, of the string whose first byte is addressed by the contents of the address field (modified if the instruction specifies) modification).

# 2.3 Type 2 = Descriptor Descriptors

Size and S fields i.e. bits 2-5, are ignored (reserved) and should be set to 1100. These function just like type 0 descriptors with size code 64 bits, and are interchangeable with the latter.

2.4 Type 3 = Miscellaneous Descriptors (fig. 15)

Bits 2 - 7 define a subtype number.

## Subtypes (numbered decimally):

32, 33 Code (Bounded, Unbounded)

Code descriptors may be used to point to the destination instructions of Jump, Call and Exit instructions only. Bits 32-63 contain the byte address of the first byte of the instruction - bit 63 is ignored as instructions are halfword aligned.

Any modifier added to the address is multiplied by 2 before addition. If subtype 32, bits 8-31 contain a bound which is used to check the modifier, if any, in exactly the same way as for type 0 and type 2 descriptors. If subtype 33, bits 8-31 may contain the identity of a microcode subroutine which may be entered after PC is set. If the microcode subroutine does not exist or if an error is encountered within the routines a jump is made to the instruction addressed by PC.

35 System Call

Bits 8-31 usually contain an entry displacement to index a

System Call Index Table. Bits 32-63 usually contain an

entry displacement to index the System Call Table indicated

by the descriptor accessed from the System Call Index

Table. System Call descriptors are only used by the Call

and Exit instructions - in the latter case as a 'link descriptor'.

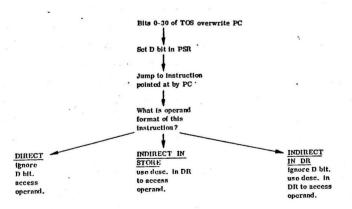

37 Escape

Escape descriptors are used to by-pass normal instruction sequencing rules. Whenever a descriptor in DR, which is being modified by MODD, or used to access information indirectly is found to be an Escape descriptor, a branch out of sequence occurs. Bits 32-63 contain the address of a word whose contents will be transferred to PC as part of the escape action. Bits 62, 63 are ignored so the address is word-aligned. Escape descriptors are not modified. Bits 8-31 are ignored (reserved).

40, 41 Semaphores (Bounded, Unbounded)

These descriptors are used to point to semaphore locations in store. The format is similar to a type 0, size code 5

Issue 1

descriptor and modification rules are the same.

The descriptor is restricted to use with INCT and TDEC instructions. The effect of use with other instructions is undefined. The descriptor must not be used to access the stack segment.

Access to the word pointed at by the descriptor is forced by hardware to bypass slave storage and is implemented by a Read Hold, Write Hold combination so as to prevent access to the store location while the word is being modified. If slave storage is present, use of this descriptor clears the operand slave store of items from segments marked non-slaved (NS).

#### 63 Null

A null descriptor is used to provide the NIL option when a descriptor is used as an optional parameter for a procedure. It is detected by the VALIDATE instruction and is invalid with all other instructions.

This facility is available at AMLI.

#### 3 OPERAND ADDRESSING AND ALIGNMENT

### 3.1 Operand Length (Primary and Tertiary Formats)

By 'operand length' is meant the number of bits in the addressed quantity on which an instruction actually operates. In the case of an instruction operating on ACC, this is usually determined by ACS, but not always - for instance in a Floating Divide Double instruction the operand length is  $\frac{1}{2}$  ACS, for a Scale instruction the operand length is 32 bits regardless of ACS. The operand length is not necessarily the same as the length of the addressed item in store. When the latter is specified by a descriptor - e.g., a 5-byte string addressed by a string descriptor, or a single bit or byte addressed by a vector descriptor with the appropriate size indication - it may be used in an instruction for which the operand length is 64 bits. The rule is that when an operand is read from store or a register, the length of the addressed item must not exceed the operand length. However, if the length of the addressed item is smaller, after the item has been read it is extended with left hand zeroes to the required length.

When an operand is written into a store location or register of different length:

- (a) If the stored item is addressed by a string (type 1) descriptor, its length must not exceed the operand length. In other cases, if the operand length is smaller, the operand is extended with left hand zeros to fill the store space.

- (b) If the operand length is greater, the operand is truncated on the left until it fits the store space.

If the source or destination stored item is addressed by a string (type 1) descriptor and its length is zero or exceeds the operand length, a non-maskable program error (descriptor) interrupt occurs. If the length of an item read from the store other than via a string

Number 6594899 Sheet 3.2

descriptor exceeds the operand length, or if non-zero bits are truncated from an operand being written to the store or to B, the operation is suppressed and a Size interrupt occurs, unless the interrupt condition is masked. If the condition is masked the operation is not suppressed; the leftmost portion of the item taken from the store is ignored in the first case, and the non-zero bits truncated are treated as zeros in the second.

The exception to this rule occurs in the case of Jump-type instructions, where the operand, which overwrites PC, is conceptually 32 bits long: however when the operand is specified indirectly via a descriptor its length in store is permitted to be 32 or 64 bits, and in the latter case the least significant 32 bits overwrite PC, the more significant 32 bits being ignored.

Type 1 descriptors are not permitted. When accessing image store locations, the operand length must be 32 bits; otherwise, the action is undefined. The operand length required by each instruction is listed with the instruction description. The operand lengths for store-to-store instructions are specified in the secondary instruction format (see section 1.12).

# 3.2 Addressing Rule

The address of an item in the store is the address of its left-most (lowest numbered) byte. Where individual bits are addressed by modified vector descriptors, the bit number, from 0 (left-most bit) to 7, is concatenated to the address of the byte.

## 3.3 Word Alignment

Operands directly addressed in the store (i.e. using the operand forms)

T, Ln, LN, PN, XN, CN and BN.

Number 6594899 Sheet 3.3

as well as modifiers and descriptors used in the corresponding indirect forms, start on word boundaries - i.e. their byte addresses are multiples of 4. This is ensured automatically thus:-

T, Ln, LN, XN,

: SF, LNB, XNB and CTB contain word

CN

aligned addresses.

PN

: the least significant bit of the sum is ignored.

BN

: the 2 l.s. bits of the sum are ignored.

Note that 64 and 128-bit items are not constrained to be on double or quadruple-word boundaries in store. Therefore such items are liable to cross page boundaries, or violate segment limits, even when the addresses of their first words have been checked and found 'legitimate' - the final address must be checked too.

# 3.4 <u>Justification in Registers</u>

In general quantities transferred from store, or as literals from the instruction format, to registers, and vice-versa, are right-justified in both registers and store locations. Sign extensions or zero filling on the left takes place according to rules stated elsewhere. Thus, in calculating the value of 'PC+N', N is assumed to be in the same units as the contents of PC, i.e. halfwords, and signed; while in calculating 'LNB + N', N is considered to be a number of words, and is unsigned, i.e. positive. An exception to this rule occurs when a stored quantity represents a virtual address, in which case it is a byte address; this particularly applies to the items transferred to PC by jump instructions. Thus for 'Load LNB' the operand is a byte number whose least significant 2 bits are ignored, rather than a word number.

3.5

#### Primary and Tertiary Format Operands

#### Literals

The operand forms n and N cause the operand to be generated by extending the quantities n (7 bits) or N (18 bits) on the left with copies of their most significant bits, to the required operand length. A signed literal specified as the operand for a jump instruction will be added to, rather than overwrite, PC. Interrupt occurs if this alters the segment number in PC.

#### Image Store

The operand forms G and GB cause the 32-bit image store location indicated by N, or by the contents of the B register to be accessed.

#### Top of Stack

The operand T causes the item at the top of the stack (of length = operand length) to be used as operand, and SF to be decremented by the operand length in words. Program error interrupt occurs if this causes SF to become < LNB.

For Store-type instructions the result is stored as a new top-of-stack item causing SF to be incremented. If storing the result violates the stack segment limit a virtual store interrupt occurs.

#### <u>B</u>

Causes the 32-bit contents of B to be read (extended with zeros if necessary) or overwritten.

## Directly-Accessed Items in Store

For the operand forms I. n, L. N, X. N, P. N, C. N and B. N. the address of the operand is formed by adding N (or n) to the appropriate pointer location, to form a byte address which is a multiple of 4.

Number 6594899 Snee: 3,5

gth of item accessed = operand length. The rules for checking this addition vary from one form to another, as shown below:-

Ln, LN : n extended with zeros; m.s. 2 bits of N must be zeros.

No carry out of LNB permitted.

X N, C N : No check

N extended with zeros.

PN: N is regarded as a signed half-word displacement.

Bits 1-17 of N are added to bits 14-30 of PC. Carry out of bit 14 of PC is checked equal to bit 0 of N, and is <u>not</u> added to bit 13, i.e. segment overflow is forbidden. The least significant bit of the sum is ignored. The operand

must be wholly in the current code segment.

B N : No check - N is extended with zeros and is regarded as

a word displacement. The 21.s. bits of B are ignored.

Failure of any check causes an interrupt.

# Indirectly - Accessed Items in Store

The operand is accessed via a descriptor at the specified location.

There are two cases: in one case the descriptor is accessed like a directly accessed operand (i.e. as described above but of length = 64 bits) - the descriptor may be modified by the contents of B - and in the other case the descriptor is already in DR and may be modified by a directly accessed quantity. In both cases the descriptor is left in DR unmodified, after use, Unless otherwise stated, the descriptor may be of types 0, 1, 2 or Escape for any primary instructions.

For jump instructions (including Call) the same rules apply except that type I descriptors are not allowed, and the size code in a type 0 descriptor may only be 32 or 64 bits. For a 'Call' instruction 'Code' or 'System Call' types are also permitted. If the descriptor is of Escape type a jump out of sequence occurs.

Number 6594899 Sheet 3.6

lecua

Modifiers, whether obtained as directly accessed quantities or from B, are 32 bit quantities. When N is used as a modifier it is extended with zeros on the left. The modifier is added to the contents of the address field - other fields are unaffected.

When the modifier is added, a full 32-bit addition is performed, overflow due to scaling or to the addition being ignored. When bound checking is required (BCI not set) the most significant 8 bits of the modifier before scaling must be 0's and it must be less than the contents of the bound field, otherwise bound check interrupt occurs.

The checks for the directly-accessed items in store apply when any of these items is used as a descriptor or modifier. The rules for accessing and aligning operands are given in 3.1. Modifiers or descriptors taken from the top of the stack (using the forms given by k" = 6) cause SF to be decremented by 1 or 2 words, respectively.

An instruction may overwrite store locations which contained parts of the descriptor or descriptor modifier that it used to address its operand. This includes cases where the descriptor or modifier was the top-of-stack item and the instruction (e.g. Remainder Divide, or Stack-and-Load types) causes something to be stacked, though the operand itself is not on the stack.

# 3.6 Secondary Format Operands

The secondary format is only used by store-to-store functions. ACC may contain a source descriptor and DR contains the destination string descriptor (an Escape descriptor may be used in place of the latter).

#### 4 STACK INSTRUCTIONS

## 4.1 Accessing the Stack

This chapter deals with the instructions which access the stack.

Figure 16 should remind you of what the stack looks like - it is a last-in, first-out storage area which is 32 bits wide, i.e. it expands and contracts in steps of 32 bits (one word). The stack can be addressed by means of a number of hardware registers:-

<u>SF - STACK FRONT</u> (16 bits) may be regarded as a pointer, relative to the base of the stack, to the first unoccupied word in the stack. The instruction code allows for the removal of the top item from the stack, or the addition of a new item to the top of the stack - these operations automatically cause the contents of SF to be decremented, or incremented, by the appropriate number of words. SF may also be altered by an instruction which allows a specified number of locations to be added to, or deleted from, the stack. Since SF is only a relative pointer it ceases to have significance in another stack.

LNB - LOCAL NAME BASE (16 bits) contains the word address, relative to the base of the stack, of the first location in the local name space of a procedure. Again it does not have any significance outside its own stack. The quantity in LNB is always less than that in SF. The order code provides facilities for addressing items in the local name space relative to LNB.

There is an additional register XNB - EXTRA NAME BASE (30 bits) which may point to a word within the stack: however, since the length of XNB is 30 bits, it is not restricted to pointing within the stack-it may also be used for directly addressed off-stack areas. The order code allows for the addressing of items relative to XNB.

The <u>TOP OF STACK (TOS)</u> item may be 1, 2 or 4 words long - it is the programmer's responsibility to keep track of the data items used

Number 6594899 Sheet 4.2 Issue 1

and to ensure that the correct operand length be used in all operations.

For stack instructions the following restrictions apply:-

- 1. SF must always be greater than LNB.

- 2. Addressing below LNB i.e. (LNB n) is not possible.

- 3. SF is not permitted to overflow into another segment.

Thus we note that we cannot unstack below LNB and cannot obtain access to another local name space.

Now we are going to tackle each instruction in the order code in turn. For each instruction, there is a mnemonic code assigned, which is shown in brackets and this is followed by the function code in hexadecimal representation. The full instruction set is shown in Appendix 1.

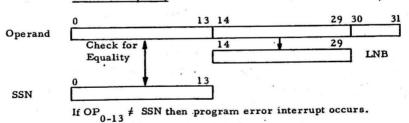

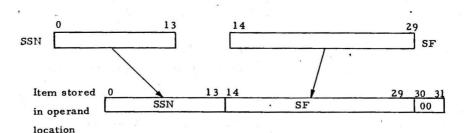

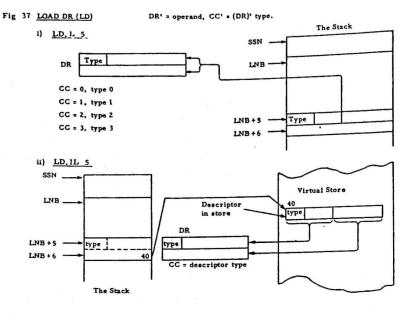

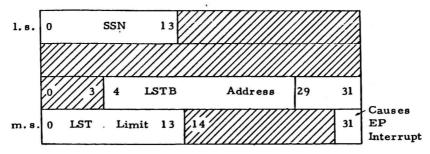

#### 4.2 Load LNB (LLN) #7C (see fig 17)

Operand length : 32 bits

Description : Bits 14-29 of the operand are loaded to LNB.

Bits 30, 31 are ignored. Bits 0-13 are checked equal to SSN. The new value of LNB is checked

to be less than SF. LNB is unaltered if these

checks are not satisfied.

CC : Unaltered

Program errors: Operand address errors. Bits 0-13 not equal

to SSN (see 12.4/8.2).

Bits 14-29 > SF (see 12.4/8.3)

Number 6594899 Sheet 4.3

Fig 16 THE STACK

# Hardware Registers

SSN = Stack Segment Number (14 bits)

LNB = Local Name Base (16 bits)

SF = Stack Front (16 bits)

XNB = Extra Name Base (30 bits)

Only XNB can point outside as well within the Stack, the rest can only point within the Stack.

TOS = Top Of Stack (item).

32 bits

Fig 17 LNB - LOAD AND STORE INSTRUCTIONS

LOAD LNB (LLN)

If LNB >SF then program error interrupt occurs.

Number 6594899 Sheet 4.4

Issue 1

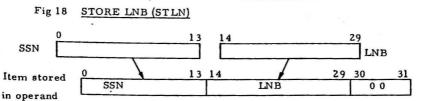

4.3 Store LNB (STLN) #5C (see fig 18)

Operand length : 32 bits

Description : The contents of LNB, expanded to a 32-bit

byte address by concatenating the contents of SSN on the left and 2 zero bits on the right, is stored. This instruction will usually be used to

'stack' the contents of LNB prior to a

procedure call.

CC : Unaltered .

Program errors : Operand addressing errors

Literal operand (see 12.8/12.1)

Non-zero bits of stored item truncated. (see

12.3/6.0)

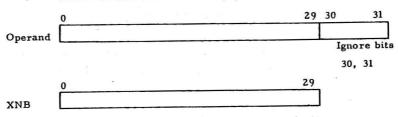

4.4 Raise LNB (RALN) #6C (see fig 19)

Operand length : 32 bits

Description : LNB is set equal to the value of SF minus the

operand. The operand is regarded as a number

of words, which must be less than the word address in SF (so operand bits 0-15 must be zero), and the new value of LNB must not be

less than the old. LNB is unaltered if these

checks are not satisfied.

CC : Unaltered

Program errors: Operand addressing errors.

Operand > SF - LNB (see 12.4/8.5)

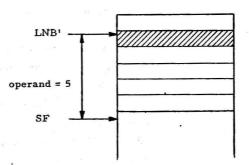

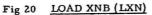

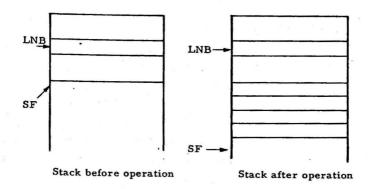

4,5 Load XNB (LXN) #7E (see fig 20)

Operand length : 32 bits

Description : Bits 0-29 of the operand are loaded to XNB.

Bits 30, 31 are ignored.

CC : Unaltered

Program errors : Operand addressing errors

location

Number 6594899 Sheet 4.5 Issue 1

Literal operands not permitted.

Fig 19 RAISE LNB (RALN) RALN 5 sets LNB equal to the value of SF minus 5.

Number 6594899 Sheet 4.6

Issue 1

#### Store XNB (STXN) # 4C

Operand length: 32 bits

Description : The contents of XNB, expanded to a 32-bit

byte address by concatenating two zero bits on

the right, is stored.

CC : Unaltered

Program errors: Operand addressing errors, Literal operand

(see 12.8/12.1). Non-zero bits of stored item

truncated.

### 4.6 Adjust SF (ASF) # 6E (see fig 21)

Operand length: 32 bits

Description : The operand, regarded as a signed number (of

words), is added to the word address in SF.

Bits 0-15 of the operand must be all the same

and must equal the carry out of the most

significant bit of SF when performing the sum, i.e. segment overflow is not permitted. The

result must be greater than LNB, SF is not

adjusted if these checks are not satisfied.

New stack locations are not cleared.

If the operand involves TOS, SF is decremen-

ted before being adjusted. If the location

pointed at by SF, after adjustment lies beyond

the stack segment limit, or lies in a page

which is not available in main store, a virtual

store condition occurs, as if that location had

been accessed. In this case SF is not adjusted

but the adjusted address must be left in the

VSI parameter. Bits 25 and 26 of the VSI parameter may indicate that either a read or

write access was attempted.

CC : Unaltered

Number 6594899 Sheet 4.7 Issue 1

Fig 21

ADJUST STACK FRONT (ASF)

e.g. ASF 4

New SF

∠ LNB causes Program error interrupt

Operand too large (segment overflow) causes Program Error interrupt

Fig 22 STORE STACK FRONT (STSF)

Number 6594899 Sheet 4.8 1 Iccup

Program errors : Operand addressing errors

New SF < LNB (see 12.4/8.6)

Operand too large (segment overflow) (see 12.4

/8.7)

#### 4.7 Store SF (STSF) #5E (see fig 22)

•

Operand length

32 bits

Description

The contents of SF, expanded to a 32-bit byte

address by concatenating the contents of SSN on the left and 2 zero bits on the right, is stored. In all cases, including those where the operand form involves the top of stack, the

value of SF as it was at the beginning of the

instruction is stored.

CC

Unaltered

Program errors :

Operand addressing errors. Literal operand

(see 12.8/12.1). Non-zero bits of stored item

truncated (see 12, 3/6.0).

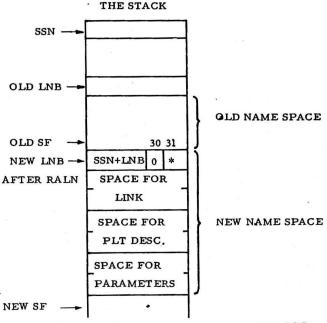

#### 4 8 Pre-Call (PRCL) #18

Operand length

32 bits

:

:

Description

a) The operand is fetched. The operand must

be a 7-bit literal.

b) If SF is even (bit 15=0), SF is incremented

by 1.

c) The contents of LNB are expanded to a 32-bit byte address by concatenating the contents of SSN on the left and 2 zero bits on the right. Bit 31 is then set to 1 if SF was incremented in b) and the result is stacked. (SF is incremented by 1). Bit 31 of LNB as stacked is tested by the EXIT instruction, to control collapse of stack.

d) The action of Adjust SF (ASF) is now

followed as described in 4.6. The operand is

Number Sheet 6594899 4.9

Sheet 4.

added to SF

CC

Unaltered.

Program errors: Operand addressing errors. New SF < LNB

(see 12.4/8.6). Operand too large (see 12.4/

8.7). Incorrect operand type (must be 7 bit

literal) (see 12.8/12.2).

The Precall instruction may be used to set up the stack in preparation for the CALL instruction (see Section 6.8). SSN+LNB are stored at TOS and a new name space created for the Link descriptor, parameters and for procedure linkage table descriptors by adjusting Stack Front by a required amount as specified by the operand. See fig. 23.

Fig. 23 PRECALL

NOTE:\* 1. For efficiency of Stack accesses on larger 2900 OCP's, if original SF is even, SF is first incremented by 1, and bit 31 of stored LNB is set to 1. This is to ensure that the items in the new name space will be aligned to an

Number

659489

Sheet

1

even-word boundary after stacking SSN+LNB at TOS.

LNB must be raised to point to TOS by use of RALN instruction before the CALL instruction. (See section 4.4).

Number 6594899 Sheet 5.1

Sheet 5.1 Issue 1'

### 5 ACCUMULATOR INSTRUCTIONS

This chapter deals with the non-computational instructions which involve the ACC.

## 5.1 Load (L) #60

Operand length : ACS

Description : The operand is loaded to ACC. UV is cleared.

CC : Unaltered

Program errors: Operand addressing errors.

# 5.2 Set ACS 32 & Load (LSS) #62

Set ACS 64 & Load (LSD) #64

Set ACS 128 & Load (LSQ) #66

Operand length : New value of ACS

Description : A new value is loaded to ACS, and the operand

(whose length is determined by the new value of

ACS) is loaded to ACC. OV is cleared.

There are three versions of the instruction, corresponding to the three possible values of

ACS.

CC : Unaltered

Program errors: Operand addressing errors.

### 5.3 Store (ST) #48

Operand length : ACS

Description : The contents of ACC are transferred to the

operand location. If the length of the latter is less than ACS, and any of the truncated more significant bits of the former are non-zero, an

interrupt occurs, ACC is unaltered.

CC : Unaltered

Program errors : Operand address errors. Literal operand (see

12.8/12.1) Significant part of operand

truncated. (see 12.3/6.0).

Number 6594899 Sheel 5. 2

tesue 1

# 5.4 Load Upper Half (LUH) #6A

Operand length : ACS

Description : ACS is doubled and the operand is loaded to

the upper half of ACC. The lower half of

ACC is unaltered. OV is cleared. ACS =

128 bits is not permitted.

CC : Unaltered.

Program errors : Operand addressing errors.

ACS = 128 bits (see 12.9/13.4)

### 5.5 Store Upper Half (STUH) # 4A

Operand length : Half ACS

Description : The contents of the more significant half of

ACC are stored in the operand location.

ACS is halved. The lower half of ACC is

unaltered.

ACS = 32 bits is not permitted.

CC : Unaltered.

Program errors : Operand addressing errors. Literal operand

(see 12.8/12.1) ACS = 32 bits (see 12.9/13.4)

Significant part of operand truncated (see

12.3/6.0).

#### 5. 6 Copy DR (CYD) # 12

Operand length : Not applicable. Literal must be specified.

Description : The contents of DR are copied to ACC. ACS

is set to 64 bits. OV is cleared. DR is

unaltered.

CC : Unaltered.

Program errors : Only universal types listed in section 12, 10.

Number 6594899 Sheet 5.3

# 5.7 Read Real Time Clock (RRTC) # 68

Operand length

l bit. Literal must be specified.

Description

ACS is set to 64 bits and the value of the hardware real-time clock is loaded to ACC.

as follows:

(i) For OCPs at AML0.

The X register is loaded into bits 0-31 of ACC.

The Y register is loaded into bits 32-63 of ACC.

(ii) For OCPs at AML1.

a) if the operand value = 0, ACC is loaded as above.

b) if the operand value = 1, bits 0-62 of ACC are set to the true binary value of the Real Time Clock such that bit 62 of ACC is equivalent to 2 \mu sec of real time.

The algorithm is:

ACC = 2.  $(x_{0-31} + (x_{31} + y_0)) + 2. y_{1-31}$

CC

Unaltered.

Program errors

Only universal types listed in section 12. 10.

## Notes:

- There are two 32 bit registers RTCX and RTCY.

- In this instruction the operand is meaningless and a literal must be specified.

RTCX is maintained by software and can be considered as a continuation of RTCY, which is a hardware binary counter.

Resolution at bit 31 of RTCY is 2 microseconds. By convention RTCX is a continuation of RTCY with bit 31 of RTCX duplicating bit 0 of RTCY. Whenever a carry from bit 1 of RTCY occurs an EXTERNAL interrupt is generated.

Number Sheet 6594899 5. 4

Issue

1

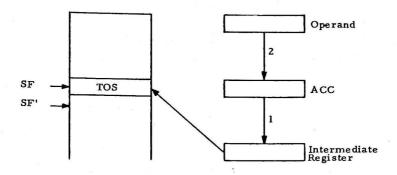

5.8 Stack and Load (SL) # 40 (see fig 24)

Operand length

ACS

Description

The contents of ACC are copied to an inter-

mediate register. The operand is loaded to

ACC, and the contents of the intermediate register are stacked, causing SF to be

incremented by ACS.

The intermediate register ensures that the

operand forms T, DT, IT and MIT are

valid. OV is cleared.

CC

: Unaltered.

Program errors

Operand addressing errors.

NOTE:- If the operand is the top of stack item, i.e. SL/T then the contents of ACC are interchanged with the item at the top of stack. OV is cleared. The operand length equals ACS for this instruction.

Number Sheet Issue

6594899 5. 5

1

Fig 24. STACK AND LOAD (SL)

#### Sequence of operation: -

- 1. Contents of ACC are loaded to an intermediate register.

- 2. Operand is loaded into ACC.

- Contents of intermediate register put on top of stack. Thus stack is incremented by the original contents of the ACC.

If the operand is T, i.e. SL T, then SF is decremented as the operand is accessed and incremented as the original contents of ACC are put at TOS. Thus SL T swops the contents of ACC with the TOS item.

STACK, SET ACS 32 & LOAD (SLSS)

STACK, SET ACS 64 & LOAD (SLSD)

STACK, SET ACS 128 & LOAD (SLSQ)

This is as STACK & LOAD except that ACS is set to the appropriate size prior to loading the ACC.

Number

6594899 5. 6

Issue

5. 9 Stack, Set ACS 32 & Load (SLSS) # 42

Stack, Set ACS 64 & Load (SLSD) # 44

Stack, Set ACS 128 & Load (SLSQ) # 46

Operand length

: New value of ACS

Description

The contents of ACC (length determined by

the original value of ACS) are copied to an intermediate register. ACS is set in a way depending on which of three versions of the instructions are used. The operand, of length determined by the new value of ACS, is loaded to ACC; and the contents of the intermediate register are stacked (causing SF to be incremented by the old value of

ACS).

The intermediate register ensures that the operand forms T, DT, IT and MIT are valid.

OV is cleared.

CC

Unaltered.

Program errors

Operand addressing errors.

5.10 Modify PSR (MPSR) # 32 (see fig 25)

PSR is the Program Status Register and controls fields such as overflow, Condition Code, ACS and Access Control Register.

Operand length

32 bits.

Number 6594899 Sheet 5. 7 Issue 1

Fig 25 MODIFY PSR (MPSR)

| 16     | 23     | 24                       | 27 | 28 | 29 | 30 | 31 |

|--------|--------|--------------------------|----|----|----|----|----|

| Progra | m Mask | Control bits<br>for MPSR |    | (  | сс | AC | s  |

PSR (Program Status Register)

Only the 1. s. 16 bits of operand are used.

If bit 27 = 1, bits 30, 31 overwrite ACS.

If bit 26 = 1, bits 28, 29 overwrite CC.

If bit 25 = 1, bits of program mask which correspond to zeros in operand bits 16 - 23 are made zeros.

If bit 24 = 1, bits of program mask which correspond to ones in operand bits 16-23 are made ones.

e.g. MPSR # 20

In this example is:-

| 24 |   |   | 27 | 28 | 29 | 30 | 31 |  |

|----|---|---|----|----|----|----|----|--|

| 0  | 0 | 1 | 0  | 0  | 0  | 0  | 0  |  |

| -  |   |   |    | -  | CC | A  | CS |  |

Thus bit 26 is set to a one and CC is set to zero.

Number 6594899 Sheet 5.8

#### Description

The least significant 16 bits of the operand are used to alter the setting of the Program Mask, Condition Code, and ACS registers, as follows:

if bit 27 is 1, bits 30 and 31 overwrite ACS. (Program error if attempt is made to set ACS = 0).

if bit 27 is 0, ACS is unaltered and bits 30 and 31 may take any value.

if bit 26 is 1, CC is set to the value in bits 28 and 29. Otherwise, CC is unaltered and bits 28 and 29 may take any value.

if bit 24 is 1, bits of the Program Mask which correspond to 1's in operand bits 16-23 are made 1's; otherwise they are unaltered. if bit 25 is 1, bits of the Program Mask which correspond to 0's in operand bits 16-23 are made 0's; otherwise they are unaltered.

bits 0-15 of the operand are ignored and may take any value.

CC

Unaltered if operand bit 26 = 0. Otherwise CC takes value specified in operand bits 28, 29.

(Note: ACS and/or CC may be set using a 7-bit positive literal operand).

Program errors

Operand addressing errors.

Attempt to set ACS = 0 (see 12.9/13.7)

Example:-

Taking an example MPSR # 20. Here bit 26 is set to a one, which enables CC to be overwritten by the value of bits 28 and 29 - these are both zeros. Thus the net result is that CC is set to zero.

Number

6594899

Sheet Issue 5. 9

5.11 Copy PSR (CPSR) # 34

Operand Length

32 bits

:

:

Description

The contents of the PM, CC and ACS fields

of PSR are stored in the operand location,

in the following 32-bit format:

Bits 0-15

0's

Bits 16-23

PM

Bits 24-27

1110 (see note below)

Bits 28, 29

CC

Bits 30, 31

ACS

Note:

Subsequent use of this operand by 'Modify

PSR' (5.10) causes PM and CC to be

overwritten, but not ACS, unless bit 27 is

made 1.

CC

Unaltered.

Program errors

Operand addressing errors. Literal operand

(see 12.8/12.1).

Significant part of operand truncated (see

12.3/6.0)

Number 6594899

Sheet 6.1

6 CONTROL AND JUMP INSTRUCTIONS

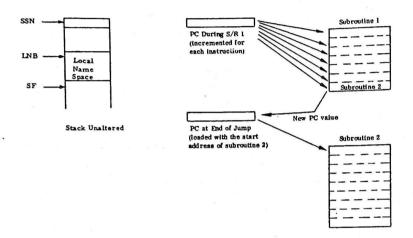

6.1 <u>Jump (J) #1A</u> (see fig 26)

Operand length : 32 bits (see note below)

Description : The operand increments or overwrites PC

causing a jump to occur.

CC : Unaltered

Program errors: Operand addressing errors for jump instruct-

ion. (see 12.6/10.0)

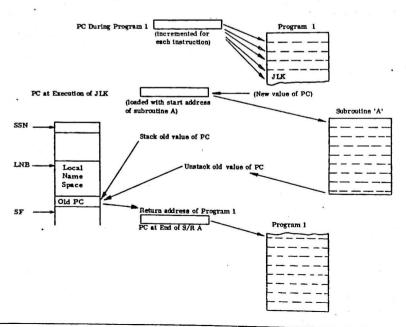

NOTE:- PC, the program counter. holds the address of the current instruction and it is incremented for each instruction. When a jump instruction is encountered in a program, PC is overwritten with the operand, which is the jump address. Fig 26. demonstrates a use of this instruction. The stack is unaltered by the jump.

The operand length should be 32 bits. If the operand is addressed indirectly via a type 0 or type 2 descriptor, the addressed item in store may be 32 or 64 bits long. In either case it is treated simply as an instruction address and not as a descriptor - if it is 64 bits long, then the most significant 32 bits are ignored.

6594899 Number 6.2 Sheet

Issue 1

Fig 26 JUMP (J)

JUMP AND LINK (JLK)

Number Sheet

6594899

Sheet 6.3

6.2 Jump and Link (JLK) # 1C (see fig 27)

Operand length

32 hits. The note under (6.1) applies

Description

The updated contents of PC are stacked as

a 32 bit byte address (i.e. with a zero bit concatenated); SF is incremented by 1.

The operand increments or overwrites PC

causing a jump to occur.

If the operand is the top-of-stack item, the updated PC and the operand are effectively

swopped.

CC

Unaltered.

Program errors

Operand addressing errors for jump instruct-

ion (see 12.6/10.0).

This instruction can be used to access a subroutine (Fig 27). The address of the jump is stored at TOS and provides the <u>link</u> back to the original program. When we have finished with the subroutine the link is removed from TOS and overwrites PC. This provides the return to the original program.

6.3 Jump on Condition Code (JCC) # 02

Operand length

32 bits. The note under 6.1 applies.

Description

If the bits of the mask field M are  $M_0$ ,  $M_1$ ,  $M_2$

$^{\&}$   $^{M}$  and if the current condition code setting is i, then operate as for the Jump instruction if, and only if,  $^{M}$  = 1;

otherwise proceed to the next instruction in sequence. Alternative condition code settings may be tested by making more than one bit

of M non-zerc.

CC

Unaltered.

Program errors

Operand addressing errors for jump

instruction (see 12.6/10.0).

This instruction uses the CC (Condition Code) Register which is set as a result of tests carried out on operands or registers. The

Number 6594899 Sheet 6.4

tertiary format is used for the instruction:-

JCC location, mask

where location is the destination of the jump. The mask field consists of 4 bits (M<sub>0</sub>, M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>) which occupy bits 7-10 of the instruction (see Fig. 13) representing the four possible values of CC.

If  $M_0$  is set to a one and GC = 0 then the instruction will cause a jump to the operand location.

If  $M_1$  is set to a one and CC = 1 again a jump will occur. Similarly for  $M_2$  and  $M_3$ .

JCC can be used in conjunction with orders such as CPB (compare B).

CPB is used to set CC as follows:-

If B = operand, CC = 0

B < operand, CC = 1

B > operand, CC = 2

so by using the instructions together:-

e.g. CPB FRED

JCC JIM, #C (mask field expressed in hexadecimal C = 1100 i.e.  $M_0 = 1$ ,  $M_1 = 1$ ,  $M_2 = 0$ ,  $M_3 = 0$ ) a jump to location will result if CC = 0 or CC = 1 i.e. if B  $\leq$  FRED.

Certain mnemonics can be used in the mask:-

E (equal to) = 8 (1000)

L (less than) = 4 (0100)

G (greater than) = 2 (0010)

Thus JCC TOM, E will produce a jump to TOM if CC = 0.

Number 6594899 Sheet 6.5

# 6.4 Jump on Arithmetic True (JAT) #04

## Jump on Arithmetic False (JAF) # 06

These instructions use the tertiary format described in chapter 1.

Operand length: 32 bits. The note under (6.1) applies:

Description : These instructions test the contents of ACC,

regarded as a floating-point, fixed point or decimal number, of DR, or of B, for one of the conditions specified by the mask field M, and a jump occurs (operand increments or overwrites PC) if the specified condition is true (first version) or untrue (second version). Otherwise the next instruction in sequence is

obeyed.

ACC, DR, B and OV are unaltered.

CC : Unaltered

Program errors: Operand addressing errors for jump instruct-

ion (see 12.6/10.0).

The table of mask conditions is shown in fig 28.

e.g. JAT ALAN, #4

will produce a jump to location ALAN if the ACC regarded as a fixed point number is zero. Note that JAF ALAN, #4 will jump to ALAN if ACC #0.

JAT and JAF do not use the CC register (unlike JCC).

# 6.5 Decrement B and Jump if Non Zero (DEBJ) # 24

Operand length : 32 bits. The note under (6.1) applies.

Description : 1 is subtracted from B. If the result is non-

zero a jump is made, the operand incrementing

or overwriting PC. If the result is zero no jump occurs and the next instruction in

sequence is obeyed. In either case the

decremented value is left in B. If B originally

contained - 2<sup>31</sup> OV is set, 2<sup>31</sup> - 1 is left in B,

Number 6594899 Sheet 6.6 Issue 1

Fig 28 JUMP ON ARITHMETIC TRUE (JAT) (# 04)

JUMP ON ARITHMETIC FALSE (JAF) (# 06)

| MASK |                                |

|------|--------------------------------|

| 0    | ACC = 0                        |

| 1    | ACC > 0 Floating Point Mode    |

| 2    | AGC < 0                        |

| 3    | Undefined                      |

| 4    | ACC = 0                        |

| 5    | ACC > 0 Fixed Point Mode       |

| 6    | ACC < 0 (Undefined if ACS = 3) |

| 7    | Undefined                      |

| 8    | ACC = 0                        |

| 9    | ACC > 0 Decimal Mode           |

| A    | ACC < 0                        |

| В    | DR Length (bits 8-31) = 0      |

| С    | · B = 0                        |

| D    | в> 0                           |

| E    | B< 0                           |

| F    | OV Set                         |

JAT ALAN, # 4 will produce a jump to location ALAN if the ACC (regarded as a fixed point quantity) = 0.

JAF ALAN,# 4 will jump to ALAN if ACC ≠ 0.

Note JAT, JAF do not use CONDITION CODE.

Number 6594899 Sheet 6.7

and interrupt occurs unless the condition is

masked; otherwise OV is cleared.

If the operand form uses B, the jump location

is undefined.

CC : Unaltered

Program errors: Operand addressing errors for jump instruction

B overflow (unless masked) (see 12.1).

6.6 Out (OUT) #3C

Operand length: 32 bits.

Description : This instruction causes a class 9 interrupt to

occur. The operand is left as the 32 bit

interrupt parameter on the new stack. ACC, B, and (unless operand access is indirect) DR are

unaltered.

CC : (Dumped value) unaltered.

Program errors: Operand addressing errors.

6.7 <u>Idle (IDLE) # 4E</u>

Operand length : Not applicable. Literal must be specified.

Description : This instruction causes instruction sequencing

to be suspended until an interrupt (of any class)

occurs.

The value of PC dumped on interrupt points to the next instruction in sequence. The instruction makes no reference to store or registers

if the operand is a literal.

CC : Unaltered

Program errors: Only universal types listed in section 12.10...

Fig 29 CALL (CALL) (# 1E)

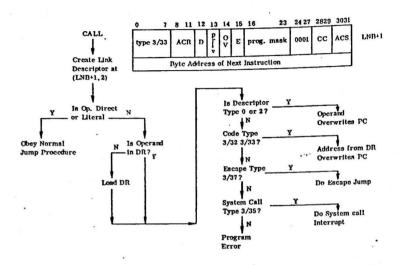

# 6.8 Call (CALL) # 1E (see fig 29)

Operand length

32 bits.

Note: If the operand is addressed indirectly via a type 0 or type 2 descriptor, the addressed item in store may be 32 or 64 bits long. In either case it is treated simply as an instruction address, not a descriptor (so neither Call nor Escape mechanisms can be invoked) and, if 64 bits long, its more significant bits are ignored. If the operand is addressed indirectly via a code descriptor, the address in bits 32-63 of the code descriptor is unbounded a microcode routine may be entered when the jump is made.

Number 6594899 Sheet 6.9

## Description

This instruction is used to enter procedures,

A link descriptor specifying the location to

return to on exit is generated and loaded into

(LNB+1) and (LNB+2). The operand increments

or overwrites PC causing a jump to occur.

If SF

LNB + 2, the link descriptor is not

stored and the instruction terminates with

a program error interrupt.

The link-descriptor is of unbounded Code

Type and consists of:-

In (LNB + 2);

The byte address of the next instruction (i.e. the length of the Call instruction added to the contents of PC, with a zero bit concatenated at the less significant end).

In (LNB + 1);

Bits 0 - 7

: 1110000î (Type 3, sub-

type 33)

Bits 8 - 11 : ACR

Bit 12

: D

Bit 13

: PRIV

Bit 14

: ov

Bit 15

Bits 16-23

: Program mask

Bits 24-26

: Zero

Bit 27

: 1

Bits 28, 29

: CC

Bits 30, 31

: ACS

Number 6594899 Sheet 6.10 Issue 1

If the address form is indirect the descriptor, which is left in DR, may be one of the following types:

a) 0 or 2

: no special action

b) Code

the address in the

descriptor itself, possibly modified,

overwrites PC.

c) System Call

: An interrupt is

performed. If the descriptor is modified, the modifier is

accessed but no

modification takes place (eg, if the modifier is

TOS, SF will be dec-

remented).

d) Escape

An escape action is .

performed (LNB+1,

+2) will be undefined.

If the operand is accessed directly from (LNB+2) or via a descriptor in (LNB+1) the result is undefined. If the operand is accessed indirectly, system software may intervene to decode a system call descriptor and in this case the contents of ACC, B and XNB must be regarded as undefined.

CC

Unaltered.

Program errors

Operand addressing errors for Call instruction.

(see 12.6/10.2)

$SF \leq LNB + 2$  (see 12.8/12.5).

NOTE: See section 4.8 for description of Precall Instruction.

Number 6594899 Sheet 6.11 Issue 1

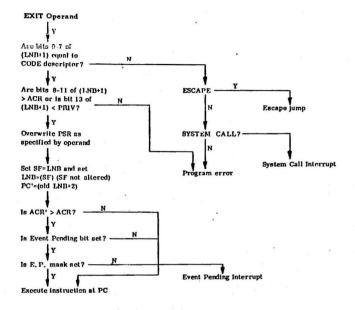

6.9 Exit (EXIT) # 38 (see fig 30)

Operand length

32 bits

Description