## COMPUTER LOGIC

The Functional Design of Digital Computers

## by Ivan Flores

How computers are put together how they work—how to use them

|   |   |   |   |    |   |    |   |                                 |   | · .          |   |   |

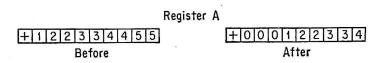

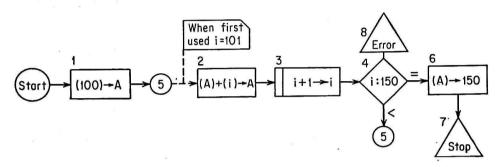

|---|---|---|---|----|---|----|---|---------------------------------|---|--------------|---|---|

| _ | + | _ | + | _  | + | -: | + | -                               | + | <u> </u>     | + | - |

| X | ÷ | × | ÷ | ×  | ÷ | ×  | ÷ | X                               | ÷ | ×            | ÷ | × |

| + | _ | + | _ | +. | _ | +  |   | + 3                             |   |              | _ | + |

|   |   |   |   | 1  |   |    |   | A COUNTY OF THE PERSON NAMED IN |   | All the same |   |   |

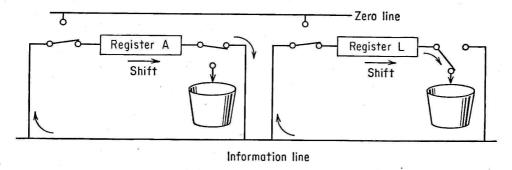

W. L. EVERITT, Editor

## COMPUTER LOGIC

### The Functional Design of Digital Computers by IVAN FLORES

This is the first book on computers to describe and illustrate with block diagrams exactly how a computer is put together and how it works. The author emphasizes the organization and functional interrelation of fundamental units and discusses these relationships from the viewpoint of operational necessity rather than mathematical logic, Boolean algebra or circuit theory.

Among the features the reader will find especially helpful are:

- the extensive treatment of two oftenneglected topics: (1) input/output and (2) control of computer function

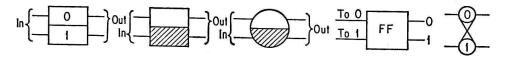

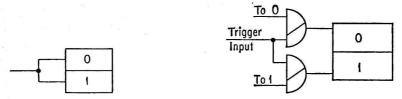

- the use of functional symbols for functional parts of equipment

- the problems that provide a means of acquiring facility with computer terms

- the final chapter that reviews in detail what happens from the time the

programmer receives the problem until the answer is ready

- the complete glossary of terms at the end of the book

(Continued on back flap)

### (Continued from front flap)

These and many more features make this book an outstandingly thorough and practical guide to the logic, the function, and the use of computers.

Whether he wants an overall picture of computers and their roles in scientific investigation and business enterprise or a detailed explanation of the how's and why's of their operation, the reader will find it in this book. Even though he has only a limited scientific background he can discover how a control unit or input/output unit functions and how the logical elements are combined to make each unit do its job.

IVAN FLORES, Ph.D., New York University, design consultant, Norwalk, Connecticut, and senior engineer at Dunlop and Associates, Stamford, Connecticut, is an active member of the professional engineering societies and a frequent contributor to their journals and lecture series.

Prentice-Hall International, Inc. 34-36 Beech Street, London, E.C.1

PRENTICE-HALL ELECTRICAL ENGINEERING SERIES

W. L. Everitt, Editor

### IVAN FLORES

Consultant

Norwalk, Connecticut

## COMPUTER LOGIC

The Functional Design of Digital Computers

Prentice-Hall International, Inc.

34-36, Beech St., London E.C.1

#### © 1960 by Ivan Flores

All rights reserved. No part of this book may be reproduced in any form, by mimeograph or any other means, without permission in writing from the publishers.

Library of Congress Catalog Card Number: 60-16719

$\frac{\text{PRINTED IN THE UNITED STATES OF AMERICA}}{16567 -\!\!-\! \text{C}}$

### PREFACE

This book considers computers first at the overall or highest level of organization and proceeds later to the lower levels of detail. We emphasize the organization and functional interrelationship of the fundamental units. These relationships are discussed from the viewpoint of necessity—they are not dependent upon mathematical logic or Boolean algebra, and they are not arrived at by circuit theory. They are, instead, discussed from the point of view of operational necessity.

A minimum is required of the reader in the way of engineering and mathematical background. The work should be comprehensible to those of some scientific training. Problems have been included to provide a means of acquiring facility with computer theory.

It is the method of the first part of the book to examine computers from the air down—a first look, a bird's-eye view from the air, is taken to see how the computer fits into the overall system of scientific investigation and business enterprise. The characteristics and specifications, then the relationship between the problem and the computer are examined. The structure and organization are investigated with regard to the large functional units, their interrelation, interdependence, and control, and an examination of programming is included. The function and composition of each unit are then pursued. The analytic approach in the first part of the book will help the reader to understand at each step the overall pattern. The second half continues, by synthesis, to build up larger and larger functional units with the goal of a complete and unified machine concept.

The interplay between design and application is emphasized. A design which keeps the user, the programmer, and the applications in mind cannot help but be superior. Similarly, the programmer who is aware of how the computer operates to carry out his instructions is able to make use of the machine.

How is each process initiated and controlled and what are the methods of coordinating the varied activities of the units which comprise the computer?

V

Programming is considered from the point of view of the programmer, the functional units of the computer, and the type of problem to be handled by the computer and the designer. The job of the programmer and the art of doing it are explained by programming a fictitious machine. The flow diagram is used as a tool. The techniques of tallying, comparison, subroutines, branch points, cycle indices, sentinels, iterations, decision making and automatic program alteration are the programming background required for effective computer design.

The computer performs arithmetic by addition, complementation, and shifting. How these are used to do subtraction, multiplication, and division is explained with examples in the decimal system so that the reader may follow with ease.

A thorough background of counting and number systems is developed in order to bring an understanding of how arithmetic is performed by the computer in its own language. This understanding is expanded to a perception of arithmetic and translation within and between different number systems. The other languages used by machines, the machine codes, and the means for performing arithmetic in machine code are discussed.

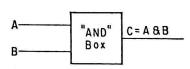

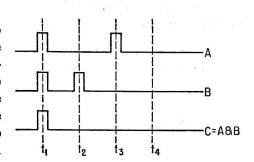

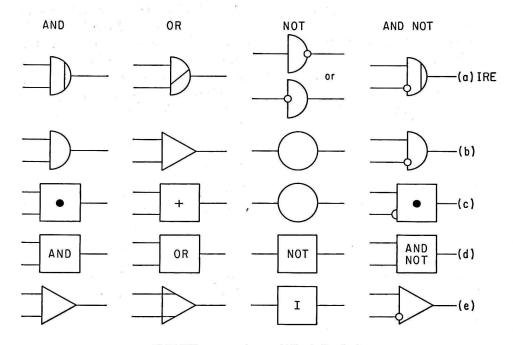

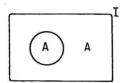

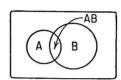

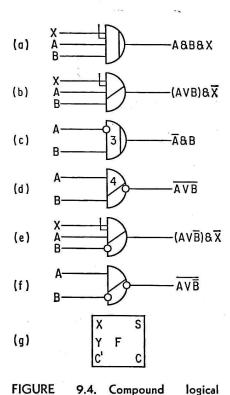

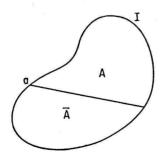

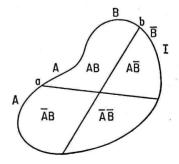

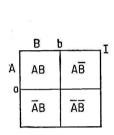

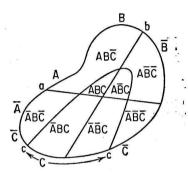

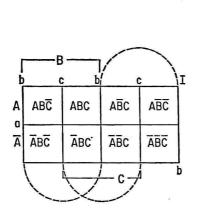

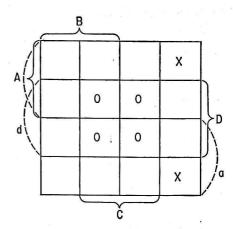

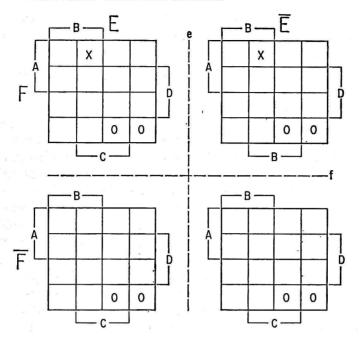

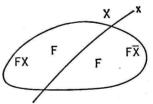

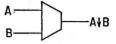

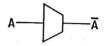

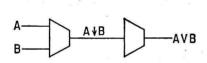

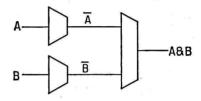

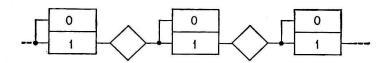

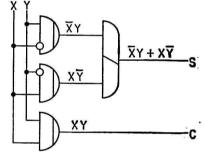

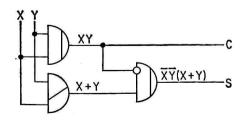

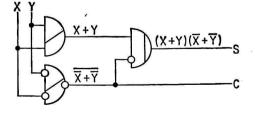

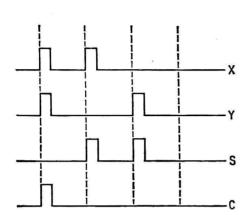

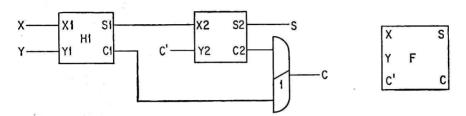

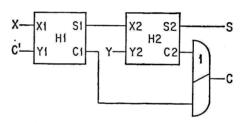

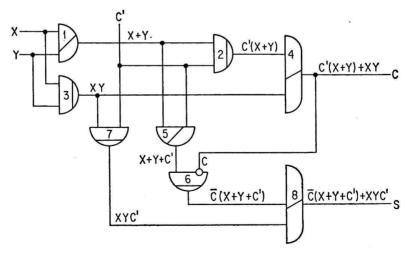

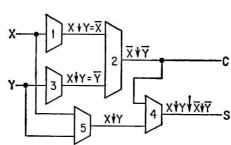

Manipulation of five kinds of elements is used to present the process of symbolic logic: propositions, geometric areas, letter symbols, functional blocks, and components. Symbols proposed by the Institute of Radio Engineers' Standards Committee are adopted. After an introductory treatment, logical methods are discussed and the binary half-adder and adder are derived; examples of its use are given. Boolean algebra is summarized. *Nor* circuits are given attention as logical blocks, along with examples of their incorporation in a computer logic.

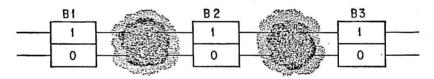

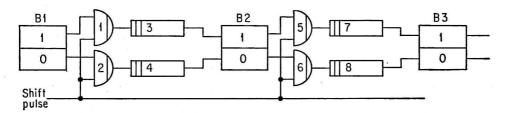

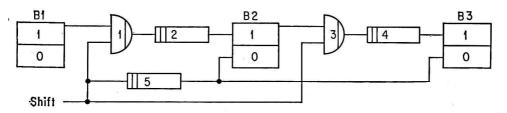

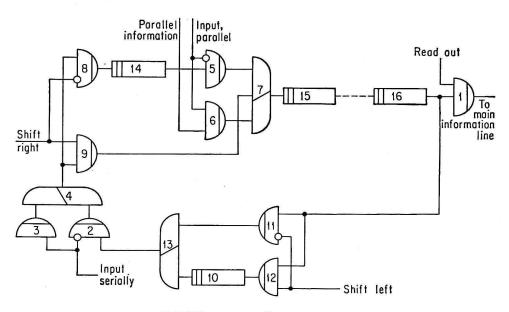

The logical construction of functional units and operational units from elementary logical units is considered, including a discussion of serial, serial parallel, and parallel adders for different codes and counting systems, accumulators, shift registers, comparators, complementors, coding units, and control units. This material comprises a fund of "unwritten art" in the computer field.

Here is where the *synthesis* approach really pays off. Starting from simple logical elements, large functional units are built up; a simple symbolic block is used to represent each large functional unit. When constructing still larger operational units it is thus possible to see and understand the relationships among the functional units because each is represented by a single block. There is not a welter of symbols all over the page to confuse the reader and obscure and complicate the reasoning.

The section on arithmetic capitalizes upon this principle. The functional and logical blocks are combined before the reader's eyes to make operational units to do each of the arithmetic operations. Before each construction, the reasoning and the elementary steps required of each

Preface vii

unit are explained both verbally and with subcommand operational flow charts. The generation of the sign of the result is also covered.

Nothing could be more important to the computer than how its functions are controlled! A chapter is devoted to the previously neglected topic of control unit operation—where the asynchronous decentralized computer control is dissected for the reader. The plan of action for the control unit is presented verbally and with operational flow charts; then each subdivision of control is analyzed. Finally, the logic to supplement the control is presented and discussed; centralized control is also examined here.

The operation of the memory is dependent largely upon the characteristics of the components comprising it. These components are investigated first and the logic necessary for memorizing and remembering follows. More attention is given core and drum memories than others because of their importance in modern computers.

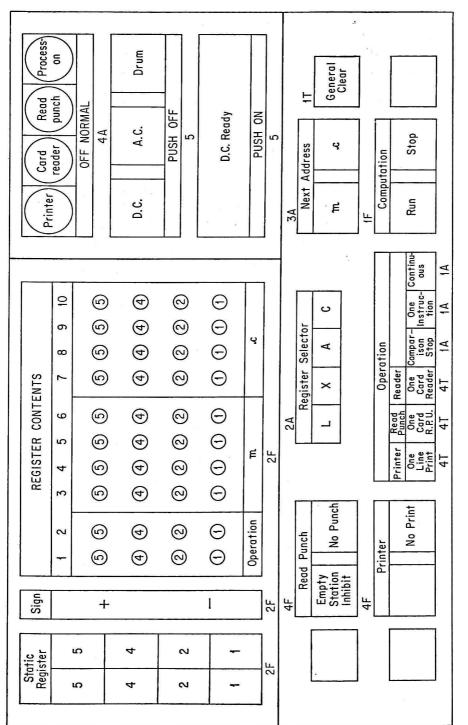

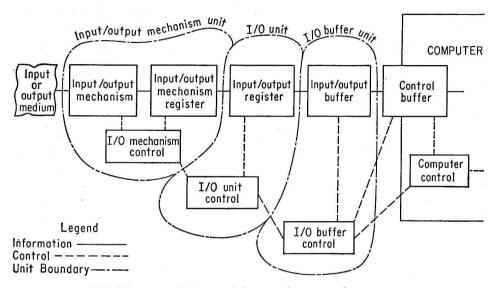

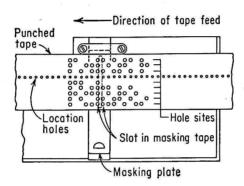

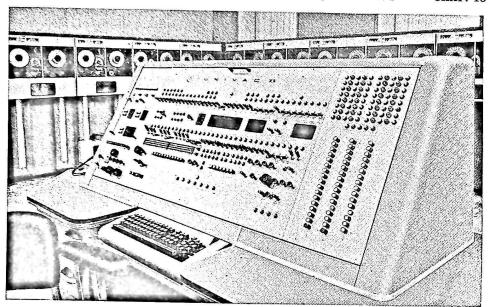

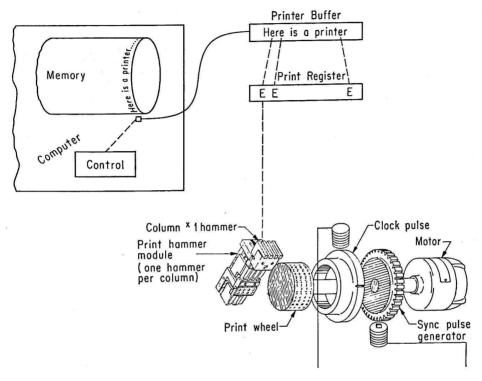

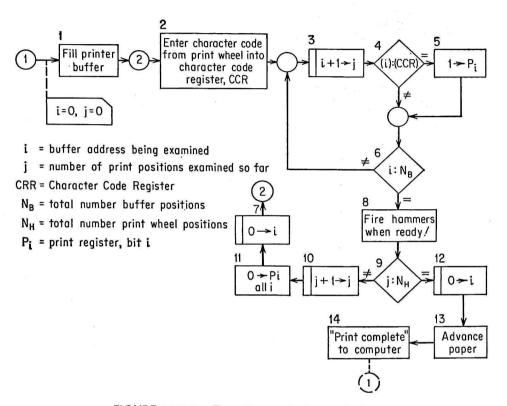

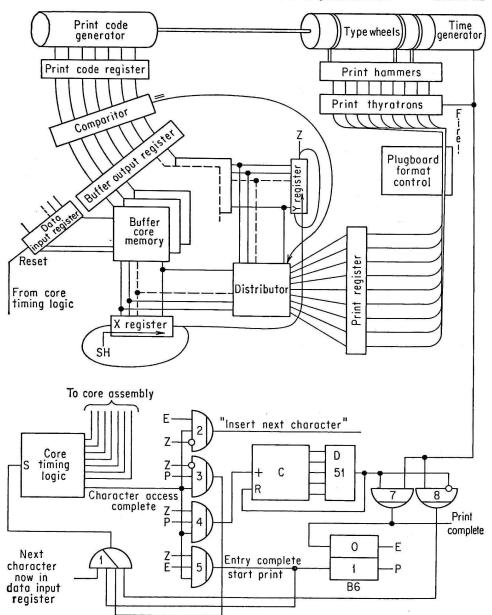

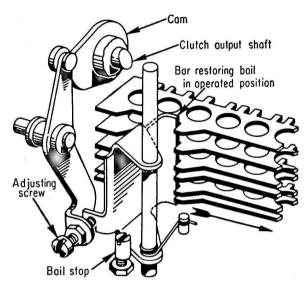

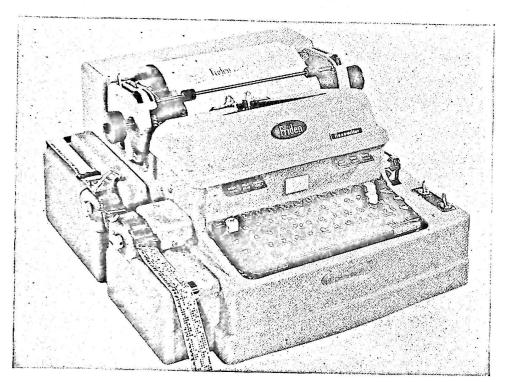

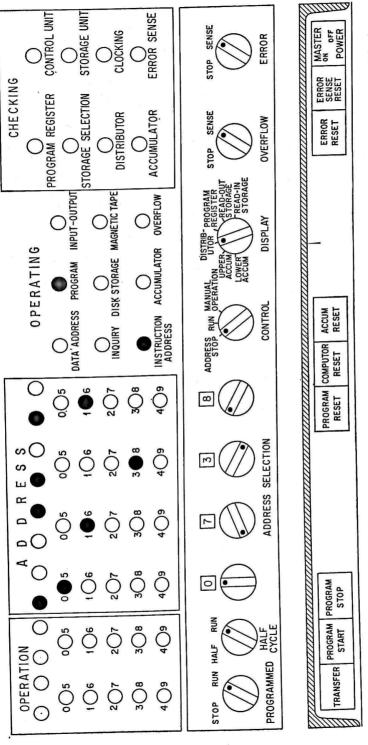

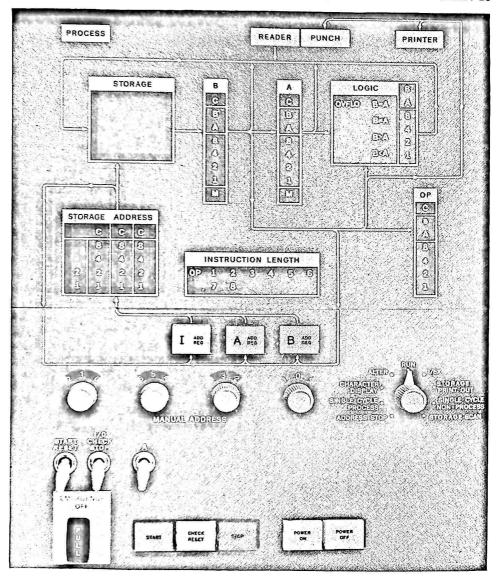

Input and output equipment have received the greatest slight in the computer literature, at least in the aspect of the logic associated with them. Maybe the author has gone overboard in his coverage of this area. But there has been so little available elsewhere that an extensive treatment is necessary to tie things together. Much mechanical detail has been included which may seem expendable. Yet, to appreciate the symbiosis of the mechanical and electronic aspects of the equipment one must comprehend its mechanical function as well as the logical principles involved. The kinds of direct communication to and from the computer are catalogued and control panels of current computers are used to demonstrate these general principles.

To encapsulate the ideas which pervade the book, a problem is presented in the last chapter. A complete analysis is made of what happens from the time the problem is given to the computer programmer until he returns the answer to whomever posed it.

The Glossary which follows the text has been culled from a number of glossaries published by the various professional computer societies. To these extracts have been added a number of definitions not found elsewhere, and some of the published definitions.

I would like to express sincere gratitude to those who have made this venture possible. First, to my wife Helen, who courageously and devotedly waded far afield into the morass of computer technology. Next, to the small band of associates, Saul Teichman, Andre Godefroy, Tom Cull, and Ralph Townsend, who painstakingly read each draft to point out where the text became unintelligible and obscure. Then to the alert and untiring efforts of the stenographic force, notably Virginia Kirchhoff and also Alice Bennett and Evelyn Davison. Lastly, to all my friends who have gracefully accepted my hibernation for the duration of this project.

## CONTENTS

| ONE   | INTRODUCTION                                                                                                                                                                                                                                                                                  | 1  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | 1.1 What is a computer? 1; 1.2 What can the computer do? 2; 1.3 How does it work? 5; 1.4 What jobs are computers used for? 8; 1.5 Analog vs. digital, 10                                                                                                                                      |    |

| TWO   | FIRST PRINCIPLES AND DEFINITIONS                                                                                                                                                                                                                                                              | 12 |

| ž ==  | 2.1 Structure, 12; 2.2 Data structure, 14; 2.3 Storage, 17; 2.4 Arithmetic, 20; 2.5 Timing, 21; 2.6 Means of instructing the computer, 22; 2.7 Checking, 23                                                                                                                                   |    |

| THREE | SPECIFYING THE COMPUTER FOR THE PROBLEM                                                                                                                                                                                                                                                       | 25 |

|       | 3.1 Introduction, 25; 3.2 The problem, 26; 3.3 Problem analysis, 28; 3.4 The computer, 32; 3.5 Analysis for the specific computer, 35; 3.6 Computer operation, 37                                                                                                                             |    |

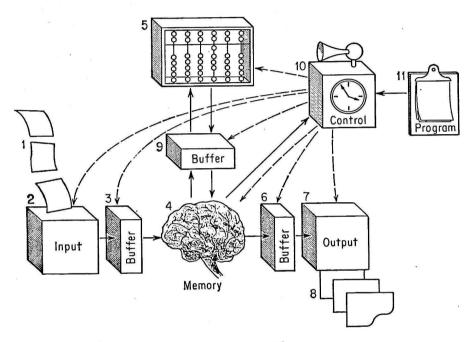

| FOUR  | THE FLOW AND CONTROL OF INFORMATION                                                                                                                                                                                                                                                           | 40 |

|       | 4.1 The plan of the computer, 40; 4.2 Operation of the control unit, 42; 4.3 Communication between the programmer and the computer, 42; 4.4 The register, 45; 4.5 Storage of information and instructions in computer memory, 47; 4.6 Illustrative machine, 49; 4.7 The control operation, 55 |    |

| FIVE  | CODING                                                                                                                                                                                                                                                                                        | 58 |

|       | 5.1 The techniques of coding, 58; 5.2 The flow diagram, 59; 5.3 Coding the addition of a set of ix                                                                                                                                                                                            |    |

### CONTENTS

### CODING (Continued)

|        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                            |     |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | numbers, 63; 5.4 Further orders, 66; 5.5 Another routine to add 50 numbers, 67; 5.6 Cycles or loops, 69; 5.7 Summary, 75                                                                                                                                         |     |

| SIX    | MACHINE ARITHMETIC                                                                                                                                                                                                                                               | 79  |

|        | 6.1 Introduction, 79; 6.2 Addition, 80; 6.3<br>Subtraction, 83; 6.4 Multiplication, 88; 6.5<br>Division, 90                                                                                                                                                      |     |

| SEVEN  | NUMBER SYSTEMS AND COUNTING                                                                                                                                                                                                                                      | 95  |

|        | 7.1 Introduction, 95; 7.2 Natural numbers, 97; 7.3 Next logical step, 98; 7.4 Bases and bundles, 100; 7.5 Decimal system, 101; 7.6 Other bases, 101; 7.7 The base two—the binary system, 103; 7.8 Arithmetic with other bases, 106                               |     |

| EIGHT  | MACHINE LANGUAGES .                                                                                                                                                                                                                                              | 110 |

|        | 8.1 Introduction, 110; 8.2 Binary decimal Codes, 111; 8.3 Excess three binary decimal code, 114; 8.4 Other four-bit binary codes—weighting, 116; 8.5 Five-bit codes—decimal binary with parity check, 117; 8.6 Biquinary code, 119; 8.7 Alphabetical coding, 119 |     |

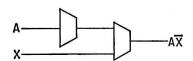

| NINE   | LOGIC                                                                                                                                                                                                                                                            | 123 |

|        | 9.1 Introduction, 123; 9.2 Fundamental postulates, 128; 9.3 Logical propositions, 132; 9.4 Blocks and hardware, 133; 9.5 Logical simplification, 135; 9.6 Examples, 140; 9.7 Nor logic, 142                                                                      |     |

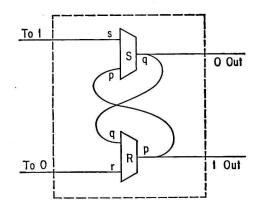

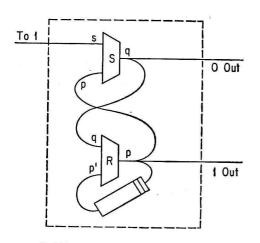

| TEN    | LOGICAL CONSTRUCTION                                                                                                                                                                                                                                             | 145 |

|        | 10.1 Bit storage and delays, 145; 10.2 The half adder, 150; 10.3 The full adder, 152; 10.4 Nor elements and adders, 159; 10.5 Shift registers, 162; 10.6 Multiple input blocks, 170                                                                              |     |

| ELEVEN | FUNCTIONAL UNITS                                                                                                                                                                                                                                                 | 173 |

|        | 11.1 Accumulators for natural binary computers, 173; 11.2 Serial-character natural binary accumu-                                                                                                                                                                |     |

### FUNCTIONAL UNITS (Continued)

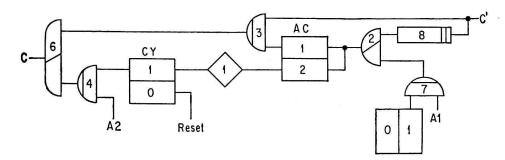

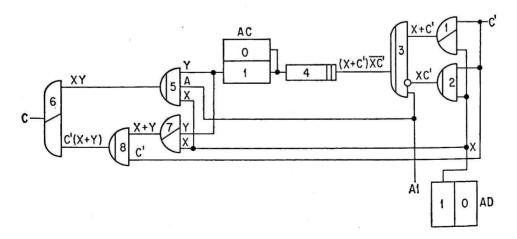

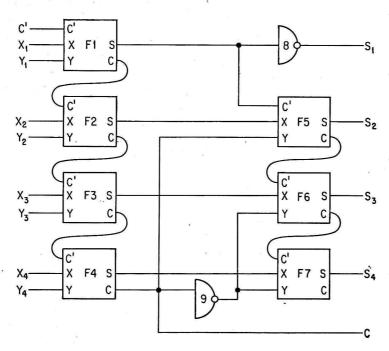

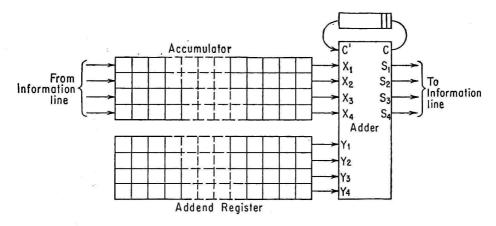

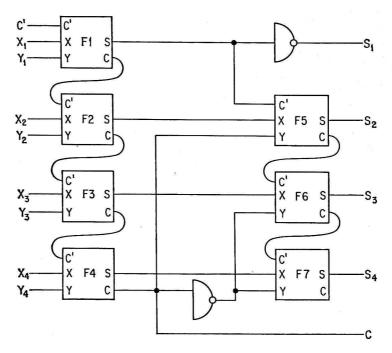

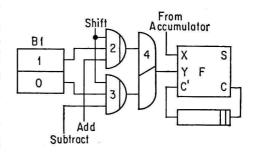

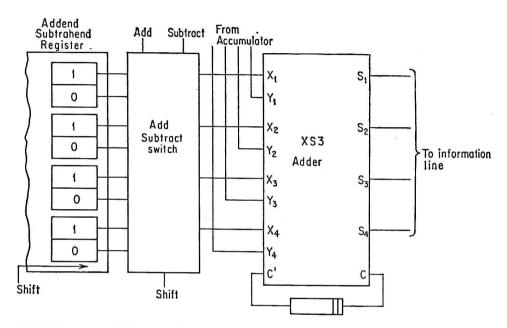

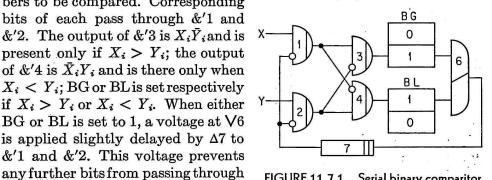

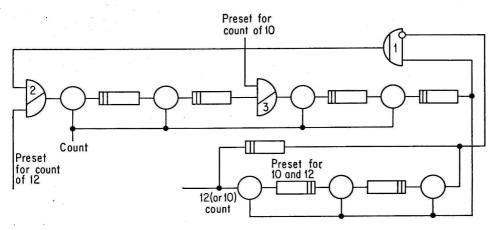

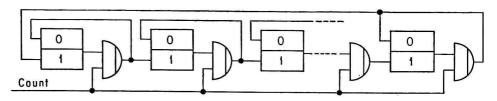

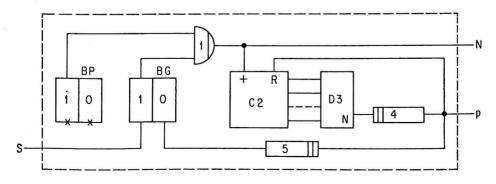

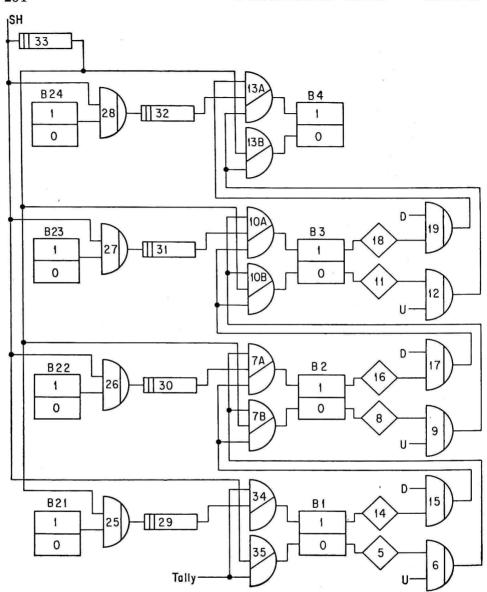

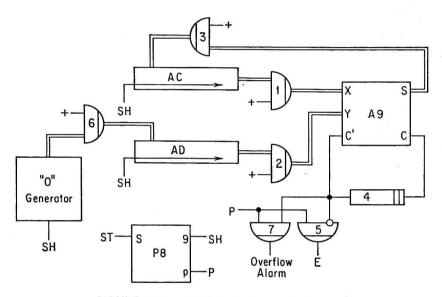

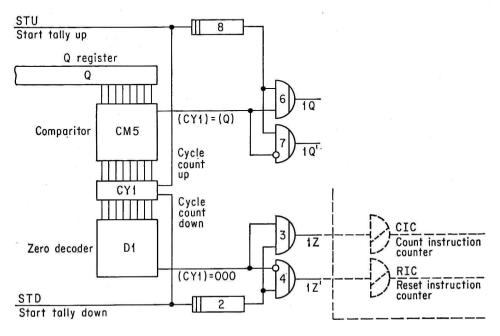

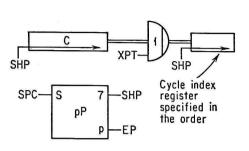

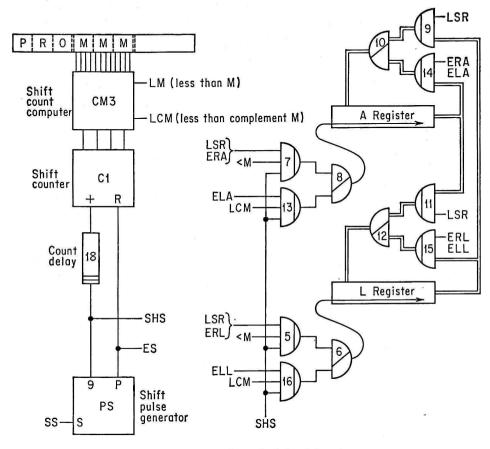

lator, 176; 11.3 Parallel natural binary accumulator, 177; 11.4 Natural binary coded decimal addition, 182; 11.5 The XS3 adder, 185; 11.6 Complementers, 187; 11.7 Comparison, 190; 11.8 Coding, decoding, encoding, 193; 11.9 Counters, 196; 11.10 Pulse-train generators, 200; 11.11 Tallies, tally registers, 202; 11.12 How functional blocks are incorporated into the control unit, 205

#### TWELVE

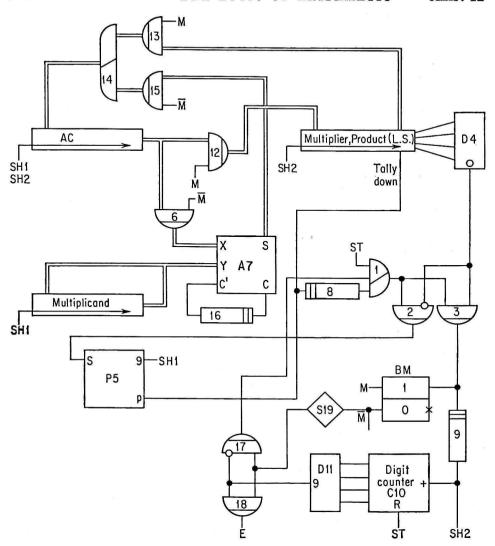

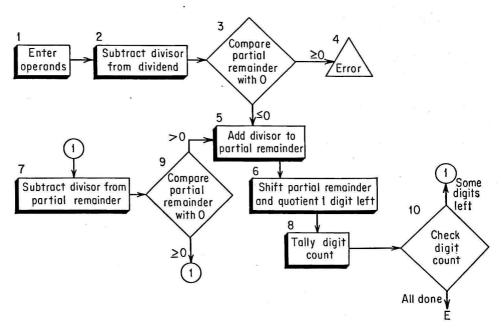

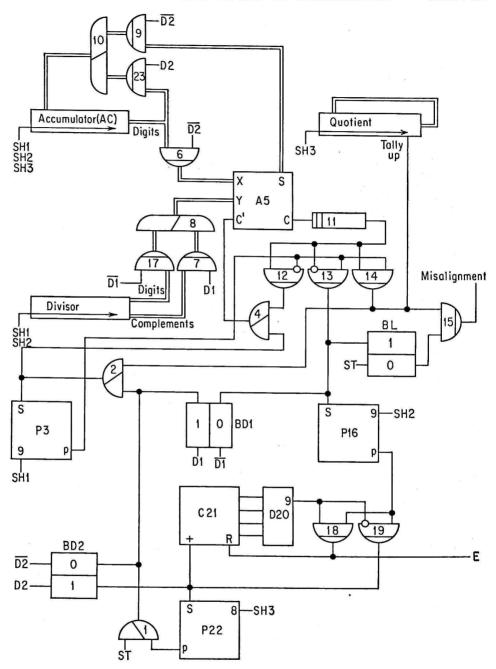

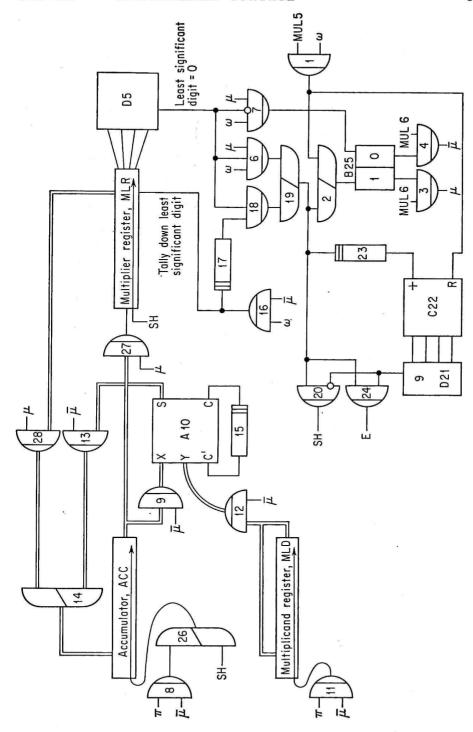

#### THE LOGIC OF ARITHMETIC

208

12.1 Introduction, 208; 12.2 Addition, 210; 12.3 Unsigned serial-digit subtraction, 213; 12.4 Signed addition and subtraction, 216; 12.5 Multiplication, 221; 12.6 Division, 225; 12.7 Signed multiplication and division, 229

#### THIRTEEN

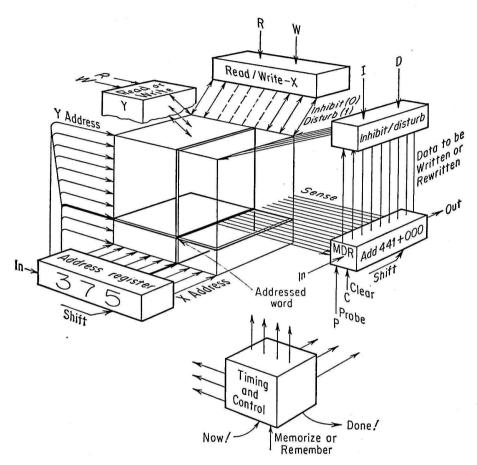

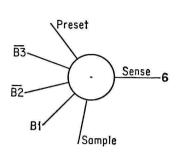

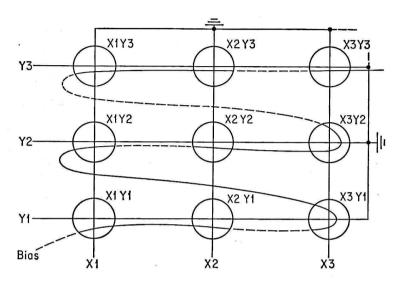

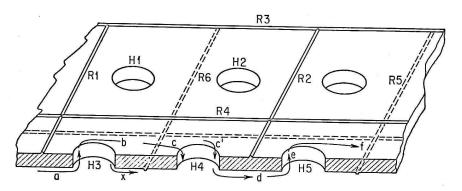

## MEMORY DEVICES AND THEIR LOGIC

231

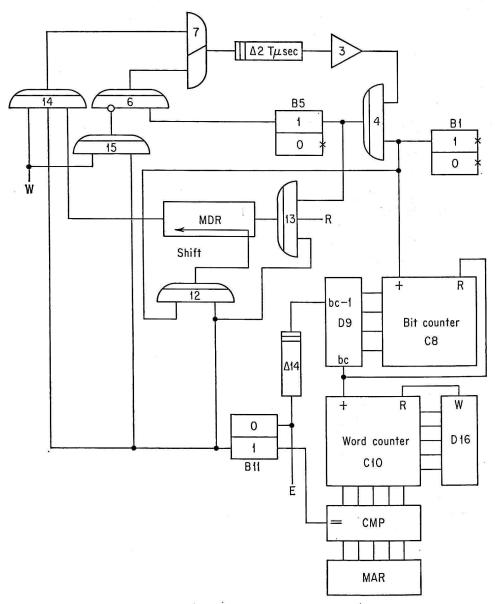

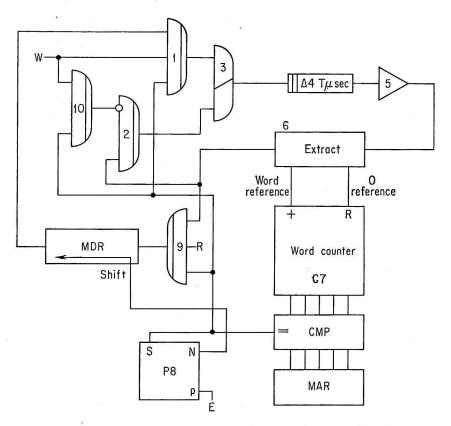

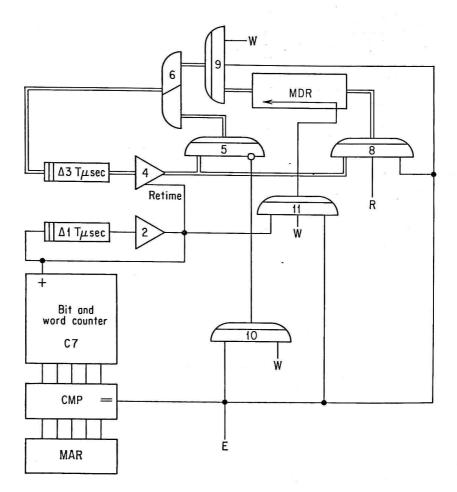

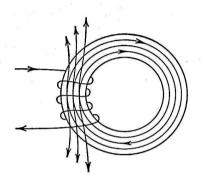

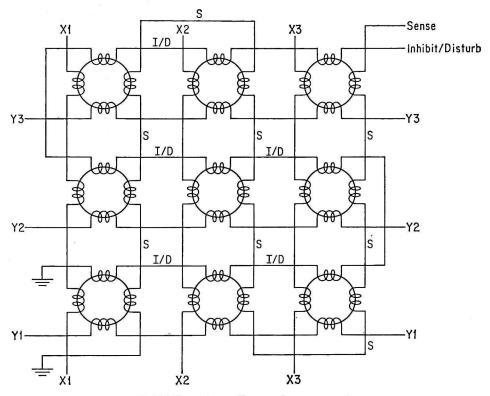

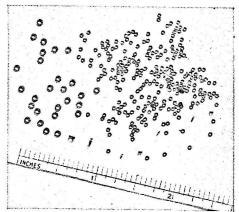

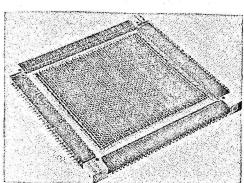

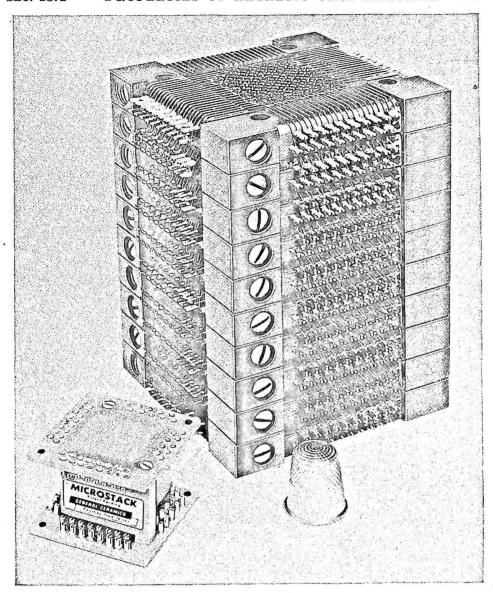

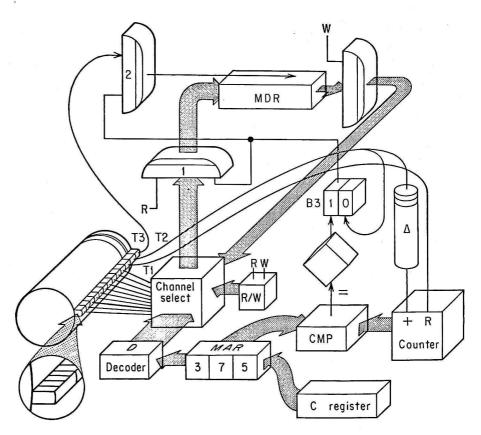

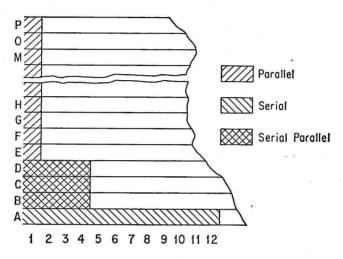

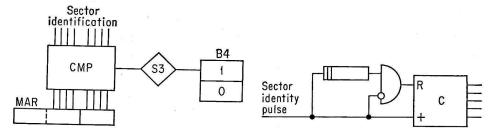

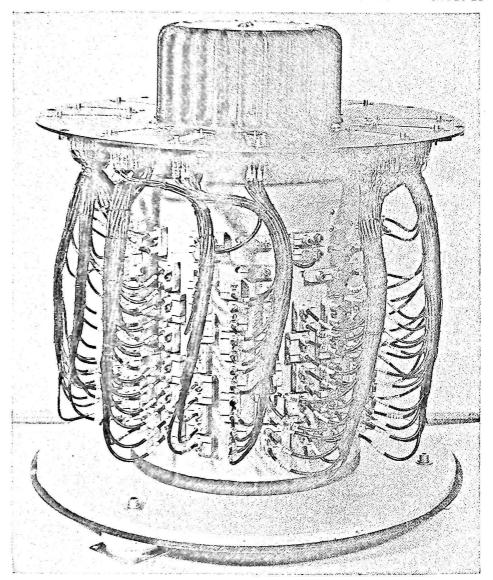

13.1 Introduction, 231; 13.2 Dynamic memories, 232; 13.3 Static storage, 240; 13.4 Properties of magnetic-core memories, 242; 13.5 Structure of the core memory, 248; 13.6 Core memory logic, 251; 13.7 Some additional remarks on core-type memories, 257; 13.8 Drum memories, 261; 13.9 Buffers and revolvers, 269

#### FOURTEEN

#### THE CONTROL UNIT

273

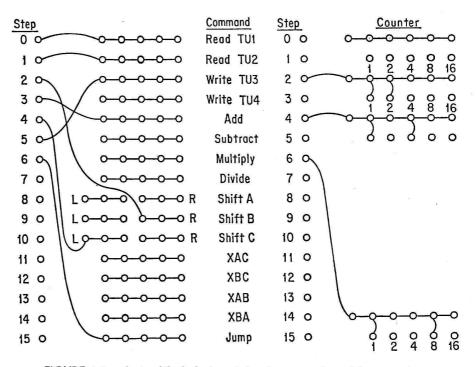

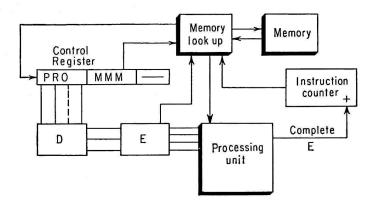

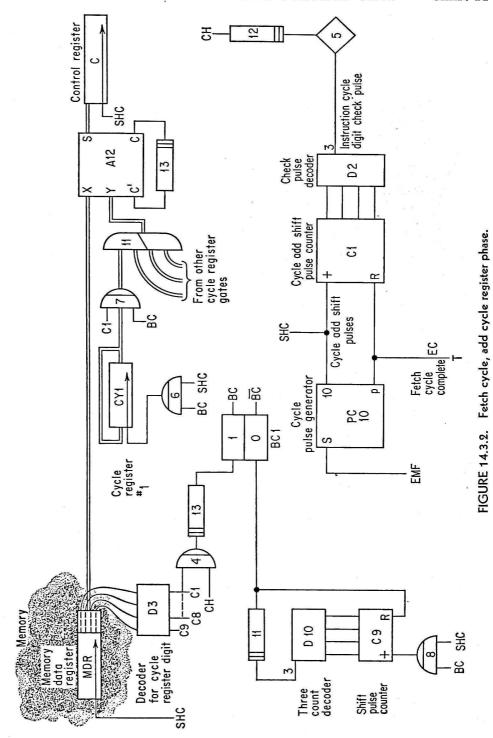

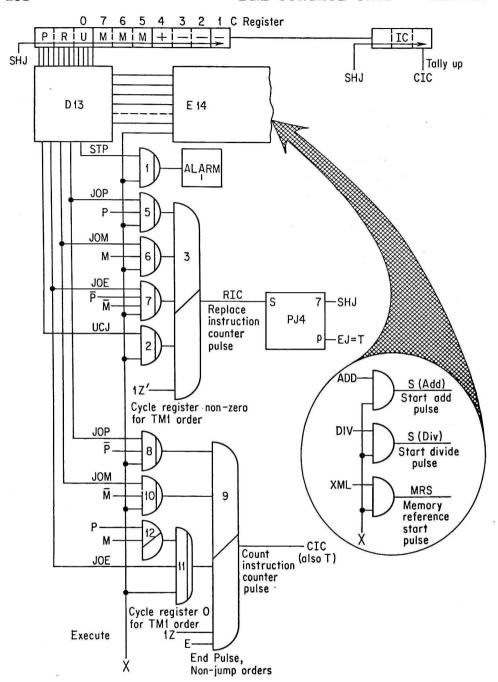

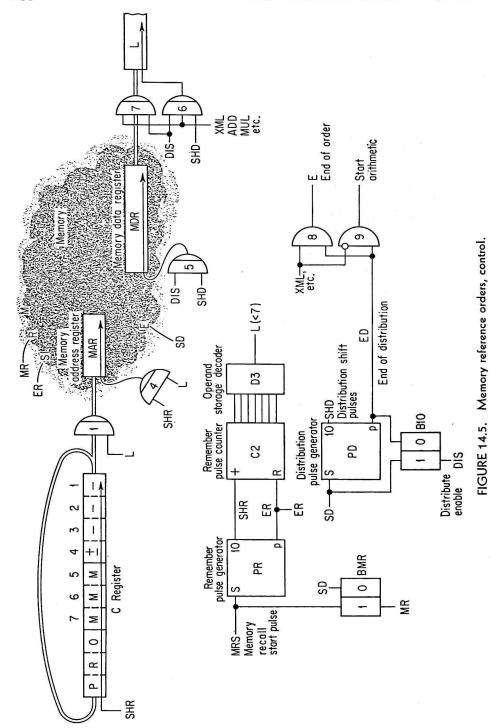

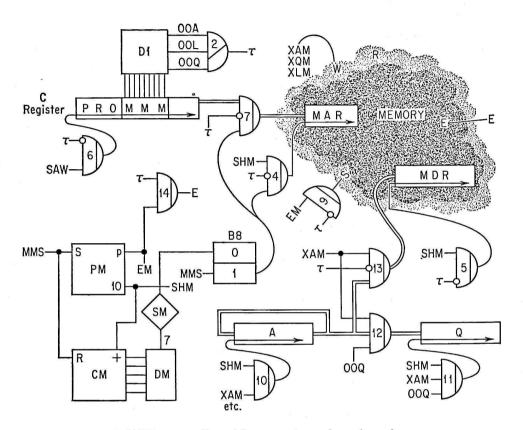

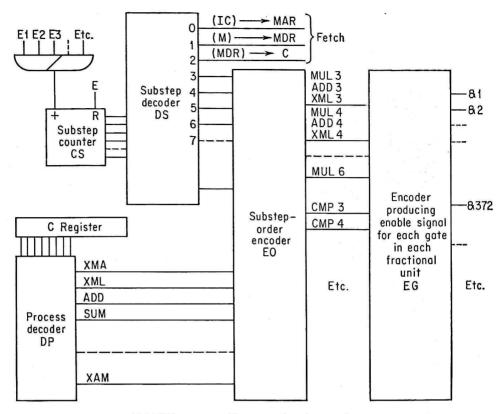

14.1 Introduction, 273; 14.2 Plan of action, 277; 14.3 Fetch logic, 280; 14.4 Jump orders, 283; 14.5 Memory reference orders, 287; 14.6 Memorization and transfer orders, 289; 14.7 Tally orders, 292; 14.8 The shift order, 294; 14.9 Centralized control, 297

#### FIFTEEN

## INPUT AND OUTPUT EQUIPMENT

305

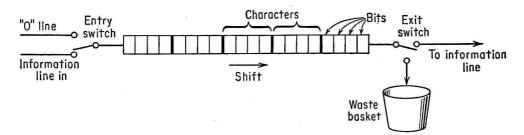

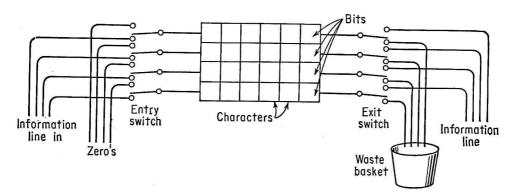

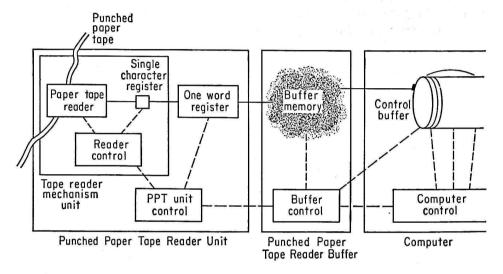

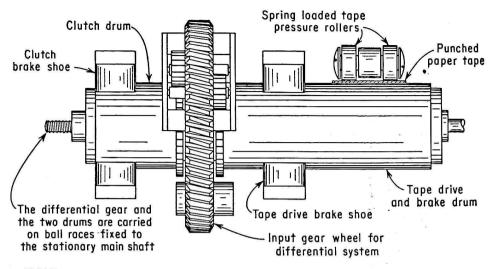

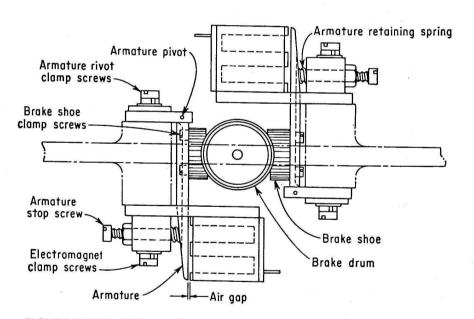

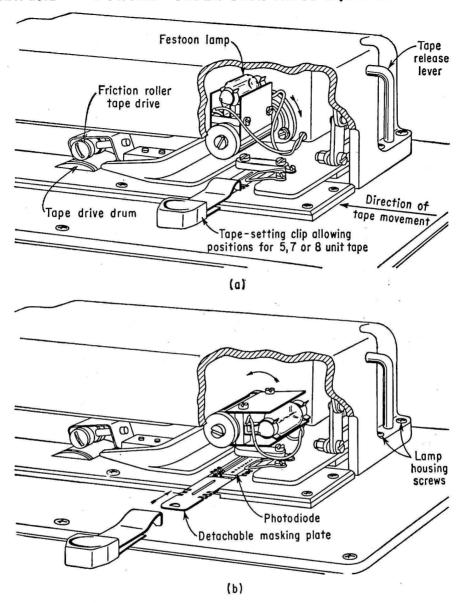

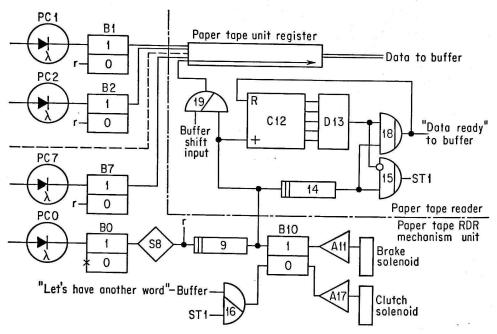

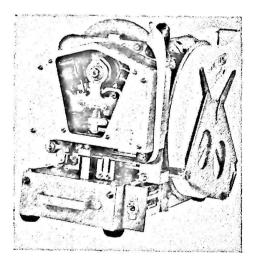

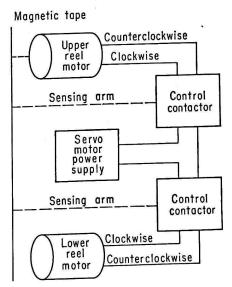

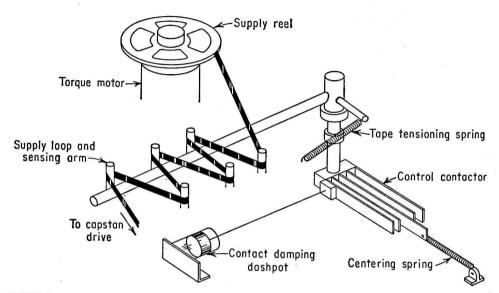

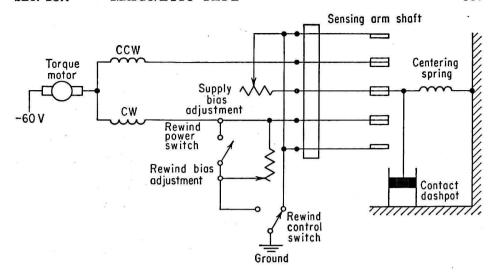

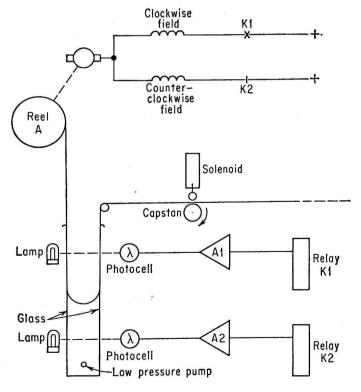

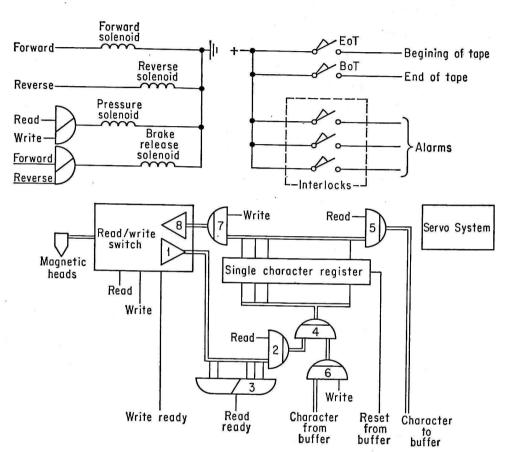

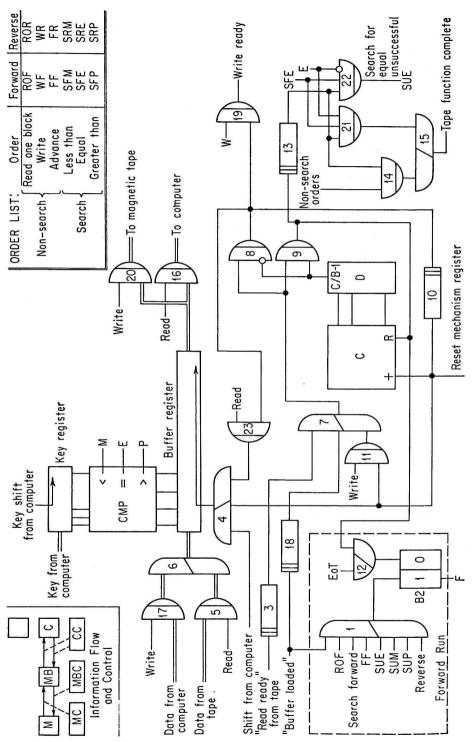

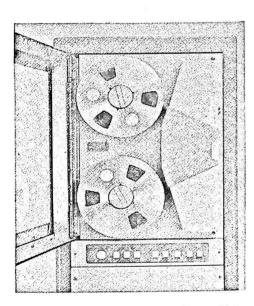

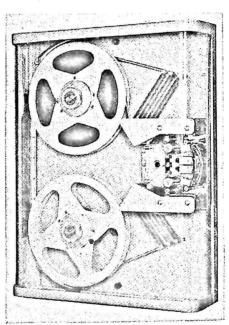

15.1 Introduction, 305; 15.2 Direct communication, 308; 15.3 Indirect communication to and from the computer, 314; 15.4 Punched paper tape input equipment, 317; 15.5 The paper tape punch, 324; 15.6 Punch cards, 329; 15.7 Magnetic tape, 331; 15.8 The high-speed printer, 344; 15.9 Typewriters, 351; 15.10 Off-line operation, 358

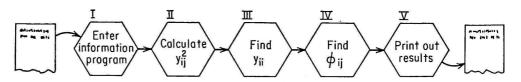

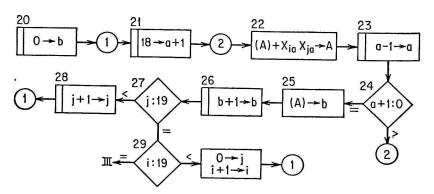

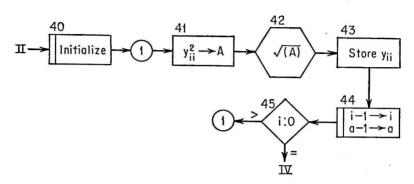

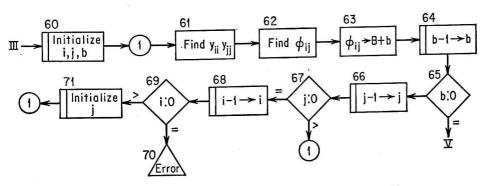

| SIXTEEN    | A PROBLEM                                                                                                                                                                                                                                                                                                                                                                                                      |     |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

|            | 16.1 Introduction, 371; 16.2 Illustrative Problem, 374; 16.3 Subdivision of the problem, 376; 16.4 More information about the polyvac, 377; 16.5 Correlation problem—find $y_{ij}^2$ , 379; 16.6 The square root subroutine, 384; 16.7 Calculation of the PHI's, 386; 16.8 Entering and removing information from the computer, 388; 16.9 Full routine, 389; 16.10 Preparation and running of the problem, 392 |     |  |

| APPENDIX A | GLOSSARY                                                                                                                                                                                                                                                                                                                                                                                                       |     |  |

|            | Definition sources, 395                                                                                                                                                                                                                                                                                                                                                                                        |     |  |

| APPENDIX B | ANNOTATED BIBLIOGRAPHY                                                                                                                                                                                                                                                                                                                                                                                         | 446 |  |

|            | Introductory, 446; Boolean logic, 446; Component and circuits, 447; Magnetics and memories, 448; Programming, 448; Block logical design, 449; Computer specification, 449; Symbols, 450; General, 450; Periodicals, 450                                                                                                                                                                                        |     |  |

| APPENDIX C | SPECIFICATIONS OF THE POLYVAC                                                                                                                                                                                                                                                                                                                                                                                  | 452 |  |

| INDEX      |                                                                                                                                                                                                                                                                                                                                                                                                                | 453 |  |

### INTRODUCTION

#### 1.1. WHAT IS A COMPUTER?

Anyone who has sufficient interest in computers to search out a book on that topic must have some idea of what one is. But somehow a fresh look at this question before plunging into a detailed study may be an advantage.

A computer, whether analog or digital, is a device for solving problems automatically. The word "automatically" indicates that there is as little human intervention as possible. Modern computers can solve problems so quickly because they are electronic devices. The types of problems computers can solve are discussed in the next section.

An important consideration is the language used by the computer. It is obvious that the computer doesn't use the same language as we do, either for receiving the problem or for solving it. If it did, we could merely tell our problem to the computer and it would answer us in spoken English.

The computer uses a unique language for solving problems. A different language may be required to get information into the computer. Thus, we may have to contend with three different languages: the English language we speak; the intermediate language used to convey information to the computer, such as the language of the holes on punched cards; and the language the computer uses for the information and for solving the problem. Let's hope this language barrier is not too great for the reader!

The computer can perform certain operations upon the information furnished it. If these operations are repeated in various sequences, different problems can be solved. Each application requires the solution of one or more problems. Thus a hierarchy exists: a few operations can solve many problems, and sets of these problems make up the applications.

In the next section the problems are discussed in answer to the question, "What can the computer do?" The operations the computer performs are discussed in Section 1.3. Section 1.4 mentions a number of applications.

### 1.2. WHAT CAN THE COMPUTER DO?

Computers in general can do a number of different things. The list we are going to make may lie beyond the capabilities of any one computer, but there are single computers that can do several of the things listed below. The more kinds of jobs we wish to have the computer do, the less efficiently it will be able to do any single job. On the other hand, if we only wish the computer to be able to do a few jobs, it may be able to do each in less time. In other words, more diverse requirements for the machine result in its taking a longer time to solve a given problem. Examples of tasks that various computers can do follow.

### Mathematical Problems

Solutions can be found for linear equations, linear differential equations, matrices, partial differential equations, polynomials, and so forth.

#### Simulation

An important function of a computer is to act as, or to create, a model of an experimental or practical situation. This can be done in two fashions:

Real-time simulation. Here, whatever should happen in a laboratory or in the field must appear to happen at the same rate within the computer.

Scaled simulation. Here the rate of time of simulation within the computer may be foreshortened, so that what would normally take a week or a month to transpire in the field would happen within a few moments in the computer. Or, conversely, the computer may perform in the period of an hour what happens within a split second in actual practice.

Both these forms of simulation are very important, and great pains may be required to get the proper scaling (ratio of computer time to actual time). An example of real-time simulation may help the reader visualize what is meant.

Take the case of a nuclear reactor. Of course, the computer does not simulate the physical characteristics of the reactor—it does not look like it, nor does it in any physical sense act like the reactor. What it does do is produce numbers which represent the energy being generated by such a reactor. The operator of the computer can then note at any moment the state of the reactor and his own capacity to control it as limited by his reaction time. He can find out how the reactor would operate, for instance, if the control rod were fully withdrawn and the reactor went critical. In the field the reactor might blow up; the computer responds by producing a very large number. If the operator at any time wished to examine closely what was happening in a short period of time, he would use scaled simulation instead of real-time simulation.

#### Control

One of the great accomplishments of computer science is its enabling computers to control things. Not only can a computer control processes and movement outside itself, but it can also control itself!

Some of the areas of control follow.

Processes. Information is supplied to a computer about the functioning of, say, a chemical plant by describing in quantitative form the pressure, temperature, rate of flow, and other data. The computer can then, by the various formulas incorporated within it, determine what adjustments should be made in each of these variables so that the processing is carried on under the proper environmental conditions. It will send back information in the form of currents and voltages or mechanical movements in order to provide compensations in such things as actuators, valves, relays, heating elements, and so forth, and thus effect a control of the processes. The use of such devices and computations provides precise chemical mixtures to produce the delicate fibers required for some of the inexpensive but beautiful fabrics manufactured today.

MOVEMENT. By the same means—by reporting to the computer information on location and rate of movement—we can have the computer produce outputs that control movement. An example of such control can be found in the new "electronic elevators" which have computers that operate to schedule them during periods of even the heaviest traffic in the world's largest skyscrapers. Also, the mechanism that enables the muchtalked-about guided missiles to reach their targets is a calculator which can compensate for the various physical phenomena which impinge upon the missile as it flies its path.

A STATE OF THE STA

ITSELF. The ability of the computer to control itself enables it to follow a given course of action until it has found a particular kind of result and then to adjust its behavior accordingly. The ability to make decisions is what makes the more advanced computer particularly effective.

### Record Keeping

One of the sections of a computer which we will discuss in more detail later is its memory or storage facility. Some computers can store large amounts of information in a small physical volume and in a form quickly accessible to the computer. The computer can insert and withdraw information from storage within an extremely short time. This enables the computer to be used for tasks such as keeping track of large inventories for commercial installations or of the entire accounts receivable or accounts payable of a vast organization.

#### Construction of Tables

Modern computers can perform many arithmetic operations in extremely short periods of time. This computational speed makes it practical and, nowadays, customary to use a computer for the calculation of mathematical and physical tables. The computer exercises control over itself by continuing to change the various look-up variables it uses in calculating the entries for a table.

### Language Translation

Because of its ability to store large amounts of information, a big computer can be and is used to translate from one language to another. In order that this translation be more than literal, various complex rules of syntax and grammar must also be stored in the memory of the computer. At the present time it is possible to translate foreign languages by computer for less than it would cost for a human to translate them. But this is so only when the input cost is not included. That's the catch! It is almost as expensive to have an operator enter the material into the machine as it is to have a person translate it!

The high-speed computer is being used now on the immense job of compiling and indexing each and every word in the recently unearthed Dead Sea Scrolls. Many of the scrolls are merely fragments. With this index containing every context in which a word appears, it is possible to do the heretofore unapproachable job of reconstructing these fragments into cogent texts; this work is now in progress.

### Function Plotting

The output of a computer can be displayed in graphic form. Thus, in addition to the normal output of the computer which might take the form of printed records or tables or the control of physical phenomena, output can be obtained on a visual basis.

### Synthesis and Analysis

An important form of drudgery taken over by the computer calls upon its ability to find the functional relation that exists within raw data. The computer can find the curve which most closely fits given data as long as it is provided with some criterion (such as "least squares") for evaluation. It can go even further than that—it can optimize variables existing in a given problem. This is done for many power companies. A power company has several generators, power lines, and busses; at any time during the day there are different loads on the different lines connected to the generators. Several different makes of computers have been put into use for the power companies to calculate which generators should be running and at what per cent of their maximum rate.

#### Limitations

It might appear that the computer is a modern magic genie. Press the button and the imp ferrets out your problem and solves it. Not so! There is much hard work involved in systematizing and translating the problem into the computer's limited language and in "telling" the computer just what and when to do things. This will be clarified in the next two chapters.

#### 1.3. HOW DOES IT WORK?

What the computer does to the information it receives is called *process-ing*. Processing is defined by enumerating the operations which are so classified.

One function of the computer is to store information. Computers have provision for temporary storage as well as for long-term storage.

The computer is capable of altering the information. This is done in two ways, known as editing and arithmetic (discussed further below).

The computer is able to move information about. Movement takes place from the input device to the computer, from the computer to the output device, and within the computer to the various sections of the computer where storage, editing, and arithmetic take place.

#### Arithmetic—What Is It?

Because we are all so familiar with how arithmetic is done, it may be difficult to put into precise terms what we require of a computer when we wish it to do arithmetic. For that reason space is devoted here to an explicit statement of what is meant by arithmetic in general.

Arithmetic can best be described in terms of symbols. Symbolically, arithmetic may be represented as " $a \otimes b = c$ " where  $\otimes$  represents one of the four arithmetic operations (addition, subtraction, multiplication, or division) and a, b, and c are information elements acceptable to the computer. The computer can deal with certain elements only. These restrictions will be discussed subsequently.

Arithmetic can be considered as a mapping relationship. For any two acceptable elements, a and b, and a process,  $\otimes$ , a third element is determined, c. The relationship is referred to as mapping because one dimension (c) is used to represent three dimensions  $(a, b, \otimes)$ .

We are more familiar with maps representing a three-dimensional locality in two dimensions. On such a map a building is represented by a dot or square. This symbol represents all the floors and ceilings and the roof and basement of the building; it also represents the pipes and the sewers below it and maybe even the subway station below them. Thus, all these things are "mapped" into one symbol. This is called a many-to-one mapping or relationship. Each of the many items (floors, ceilings, and so on) we map into one symbol (the dot or square); and conversely, the symbol stands for many different height levels.

Arithmetic is a many-to-one relationship. Thus the elements 3 and 5 and the process of addition yield the resulting element 8; the elements 4 and 4 and the process of addition yield the element 8; the elements 2 and 4 and the process of multiplication yield the element 8. There are many different possibilities or combinations of choice for the elements a and b and the process a0 that would yield the same result, 8. It may be said that these various combinations are mapped into the element 8.

Many-to-one relationships exist when there are many combinations of elements and processes that have but one resulting element associated with them, and, conversely, when one result is associated with many different combinations of elements and processes.

#### Arithmetic—How Is It Done?

The mapping view may be simplified a little if we fix a value in the process dimension and say that for a given process, any two elements may be mapped into a third element. Thus two dimensions (the numbers) are mapped into one dimension. This mapping can be performed by the use

of a table. To compute by this method would require four tables, one for each of the processes of arithmetic.

Let us examine how a table would be composed to form addition. At the head of each column would appear one of the numbers to be added; along the side of the rows would appear another list of possible numbers to be added. One would perform addition by finding the column headed by the first number to be added and the row bearing the label of the second number to be added. The sum would be found where these two intersect. Such a procedure could be followed in the adding of small numbers, but think of the size of the tables that would be required to add the numbers used in arriving at the national budget!

The other method of performing arithmetic is to incorporate some rule or procedure for generating the result within the machine. This rule would not depend upon the size of the elements a and b and hence would not impose size restrictions upon the machine.

#### The Elements Used in Arithmetic

When the elements a, b, and c discussed above are restricted to the integers, the numbers used in counting with signs attached, the computer is called a digital computer. When the restriction that the elements be integers does not exist, that is, when the elements used may be "real" numbers or even the complex numbers, the computer is called an analog computer. Chapter 7 discusses bases and counting, and the concept of integers is developed there. The above definition is quite precise, but it does not transmit the practical limitations and advantages of each system.

The outstanding quality of the integers is discreteness: there is a big gap between the values of any two consecutive elements which are used by a digital computer. Analog computers use real numbers which have the property of continuity: between any two elements it is always possible to find another element. There is no guarantee, of course, that the analog computer can distinguish this intermediate element from its neighbors.

As an example, consider the input to a computer to be a shaft rotation. The angular position would be read by the computer as one of the elements a, b, or c above. For an analog computer the shaft could rotate to any angular position without restriction and hence could occupy an infinite number of positions. For a digital computer the shaft could stop only at discrete (distinct) positions. This input would be similar to a rotary switch with positive detents at a number of positions so that the shaft can assume only one of the positions for which there is a detent. Increasing the range of the digital computer would consist of increasing the number of switch positions for one rotation of the shaft or of gearing several shafts together. No matter how much the number of positions

was increased, these positions or position combinations would still be countable and not infinite.

### Editing-What Is It?

One phase of editing is the removal or addition of information to data. For instance, the computer might deal with an employee's pay of \$40.00 as 0004000. Before this is written out in the final document, the initial three 0's must be removed and a decimal point inserted between the 40 and the 00. Similarly, it may be desired to print out the date of transaction, even though this was not included in the input data to the computer. This information may be entered into the computer once each day and then printed out with the other information as desired.

The second phase of editing is translation. Information is often handled within the computer in the form of code numbers or letters. Thus, an item in an inventory problem may be referred to in the data-handling operation of the computer by a part number. When the computer writes out information about this part, it must refer to it by name rather than by number. Similarly, during the calculation of the payroll of an employee, he may be referred to by clock number rather than by his name. In writing out his paycheck, it is necessary to refer to the employee by his name. The computer does this task of interpreting as part of the editing.

### 1.4. WHAT JOBS ARE COMPUTERS USED FOR?

In Section 1.2 a computer's functions have been discussed. In this section we will classify computer applications, some of which were mentioned earlier.

#### Commercial

High-speed computers can be used for all kinds of accounting and bookkeeping applications; notable among these are accounts receivable, accounts payable, payroll, and inventory. In these applications it is customary to keep the full records within the computer. At any time, at the accountant's discretion, a status report can be made giving the present standing of the company. During normal operation periodic reports are produced for the various accounting and executive branches of the company.

### Scientific

Any engineering or scientific enterprise runs across many applied mathematical computational problems, such as the solving of differential equations, matrices, or simultaneous equations. When a computer is available, it can be used to solve these problems.

The computer can be used as part of experimental situations. It can act as a model in either of the modes discussed previously—real-time or scaled-time operation.

The computer can be used to control and monitor experiments by incorporating relays and mechanical switches, thermostats, and so forth. A complete experiment can be automatically performed.

#### Industrial

Computers find application in industries wherever long, tedious, and repeated calculations must be made. Such use arises in design problems where complicated formulas are involved or where solutions by approximation are necessary. Trial-and-error methods can be "programmed" on an automatic computer, so that the computer will work without human assistance until it reaches the solution, at which time it will stop and announce its mission complete.

In industry there is also much use for a computer as a control and simulation element.

#### Government

One important application of a highly accurate, very compact and durable computer is in the missile guidance field. Here the computer must be sufficiently accurate to determine the compensations required for the various forces acting upon the missile, compact enough to fit into the small space allotted to it within the missile, and hardy enough to withstand the extreme temperatures and forces of acceleration applied to the missile before it reaches its target.

Air traffic control is an application where the human being has already reached his maximum performance. Here the problem concerns a number of airplanes approaching a landing field at the same time, each having a limited amount of gasoline and therefore able to stay aloft a limited time. A definite landing schedule must be allotted to each. The path of each plane must be assigned and monitored, so that as it circles the field it will not collide with other airplanes. Also, there is a take-off schedule for planes departing from the field which must be adhered to as closely as possible. Further, when emergency landings become necessary they must be given first priority and the schedule adjusted accordingly. When the problem reaches the size of that encountered at an airport as congested as La Guardia, for instance, it is impossible to remedy the situation with human operators alone within the time required for the safety of the air-

planes aloft. Additional traffic-control personnel do not seem to help—they only get in each other's way.

Still another application is in the early warning systems which gather information from throughout the continent to determine what friendly and enemy airplanes are in the area and what defense measures should be taken if enemy airplanes are sighted. Interceptors must be dispatched and monitored, anti-aircraft alerted, and so forth.

### Logical and Tactical

The areas of operational research, linear programming, and game theory have become sophisticated disciplines which require advanced theoretical background. Here, problems of marketing, logistics, and warfare can be solved on a mathematical basis but with complicated formulas best solved by trial-and-error technique. Hence they lend themselves to computational methods.

### Statistical and Analytical

Computers can be used for complicated analyses of experimental, psychological, or sociological data. Multidimensional techniques of handling such data, which formerly took months of hand computation, can be done in a short time on a computer. It is also possible to connect the computer directly to the source of data.

#### 1.5. ANALOG vs DIGITAL

In order to bring home the practical differences between analog and digital computers, a brief mention will be made of some of these distinctions.

### Quality of Information

The analog computer uses information which is continuous; that is, between any two possible readings, another reading can always exist. The digital computer uses discrete information, and it is possible to have two input readings between which no other input computer reading is found.

### Kinds of Units

It might be profitable to mention some of the kinds of units which might be used by each type of computer. If electricity were the information-bearing medium, an analog computer would examine the amplitude of the voltage; a digital computer would examine the spacing and arrangement of pulses that exist above a given minimum voltage. In considering weight, an analog computer would derive information from total weight, whereas a digital computer would consider the number of objects with a weight greater than a given minimum. With rotation, as considered previously, the analog computer would use an angle; the digital computer would consider the number of steps required to make that rotation.

#### Processes

The digital computer can perform directly only the processes of arithmetic. The analog computer can also differentiate and integrate directly.

### The Limit of the Size of the Numbers Handled

With a digital computer, the size of the numbers dealt with is limited by the number of digits which comprise the largest datum. In an analog computer the limitation is due to the range of linearity of the components. Amplifiers have such limitations. A linearity range of ten thousand to one is large, but this must be compared with the smaller digital computers which can handle with ease numbers like 9,999,999,999 (not quite ten billion).

### Accuracy

The digital computer may be provided with means for automatically detecting some types of errors it could make. The analog computer is limited by the effective noise present in its amplifiers; this noise determines the smallest increment in signal which can be positively recognized. The analog computer is also limited by the stability of the circuits which comprise it as it is subjected to power-line variation, environmental changes, and age. Component failure haunts both camps!

#### Decisions

The digital computer can make binary, ternary, and multiple-branch decisions and can alter its behavior accordingly without intervention. The analog computer depends entirely on diodes to make simple yes-no (binary) decisions. It is limited to elementary decisions which it makes on a digital basis.

# FIRST PRINCIPLES AND DEFINITIONS

This chapter will acquaint the reader with the first principles of computers, and it will introduce a large amount of terminology.

Each technical discipline has its own jargon; someone becoming acquainted with a new field will often have difficulty because its terms are completely alien to him or because a common word is used in a new and special sense. For this reason several references to glossaries are given. A comprehensive glossary (to which the reader is invited to refer frequently) has been compiled by the author and appears in Appendix A. The glossaries from which this one was compiled are listed there.

The definition of terms is emphasized because each represents a distillation of the principles encountered. Establishing a precise usage of terms early in this book permits later development to flow at a more rapid and even pace.

#### 2.1. STRUCTURE

The structure of the computer, the interconnection of the various components, the choice of the components, and the plan of operation of the computer are determined by several factors. The three factors that most

influence the structure of the computer are language, storage, and arithmetic.

#### Language

Language is the form or means by which information is communicated. The language used by the computer is not the same as that used for communication between human beings. The efficiency of the computer is greatest when the language used for manipulating information and performing arithmetic is one that conforms to the properties of the components used to construct the computer. The structure of machine languages is discussed in Chapter 8. It is important to note here that the machine language is different from human language and therefore poses the problem of translation.

Translation is necessary to change the information from human language into machine language. Direct translation from human language to machine language is often complicated and costly. Therefore, one customary sequence of operation is to translate human language into an intermediate language used by equipment in direct communication with the computer. A second translation is then made between this equipment and the computer.

The typewriter can be used to communicate with the computer. An operator uses a specially constructed typewriter such as that described in detail in Chapter 15, and performs the operation of translating English language data into key strokes. The key strokes are translated into machine language within the typewriter.

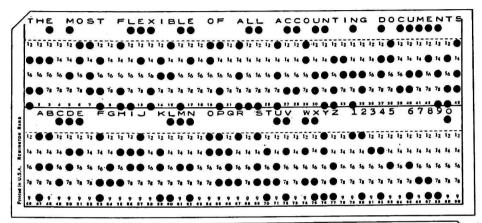

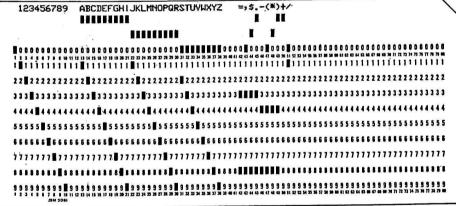

Sometimes a further intermediate step is inserted. An operator may interpret English language into key strokes which are translated into an intermediate language, and the information is temporarily stored in a punched card in the form of punched or unpunched holes (an unpunched hole being no hole at all). Equipment that reads the hole positions in the card is then attached to the computer, and the information is translated into machine language for computer consumption.

Magnetic tape is also used for temporary storage after translation of data. Here the information is transcribed into the intermediate language upon the magnetic tape and is retrieved by the computer using suitable magnetic reading devices.

Of course, taking information from the computer and putting it into an output medium such as punched paper tape or magnetic tape is the complementary process and is also required in most systems. Equipment which puts information into the computer or receives information from the computer is lumped into one category referred to as input/output equipment, or simply in/out equipment, or even more simply I/O.

#### Storage

Devices that hold information temporarily or permanently for later recovery are called storage. Such devices are sometimes classified by the length of the normal storage period. Long-term storage is called a memory; intermediate storage is referred to as a buffer; short-term storage is called a register. The quantity of information stored in a device is usually proportional to the time for which it may be stored. The memory holds a large quantity of information; the buffer holds a moderate amount; the register holds just enough for current use. The kind and quantity of such storage has an influence on the structure of the computer and its capacity and efficiency.

#### Arithmetic

Arithmetic is explicitly defined for the computer as addition, subtraction, multiplication, and division of the integers. The means used to perform arithmetic is related to the structure of the computer. A machine performing arithmetic using a table look-up will be constructed quite differently from one generating the answer by direct construction.

The arithmetic operation is also dependent upon the computer language and the arrangement of the data within the computer.

#### 2.2. DATA STRUCTURE

The data handled by the computer almost invariably represent human language data. Since the data we use in communication can be broken down into words and characters, we might expect that the computer's internal language would lend itself to a similar breakdown.

#### Characters

The character is the smallest unit of the written, English-language word. The word is the symbol for the unit of written-language intelligence. The character is the "atom" from which the "molecular" words are formed. Two kinds of characters may be considered—numbers and letters. Both may be used in human-language coded information. Thus, 5U4 is a human-language code for a particular type of vacuum tube and is composed of numbers and letters.

### Machine Coding of the Character

Presently the computer is not able to recognize or manipulate the written number or letter symbol. Therefore, it uses its own set of symbols

to compose and represent these characters. The set of symbols used by the computer to represent the written symbol is called a **code**. The symbols the computer uses to compose this code conventionally consist of "yes" or "no" information. Information of this sort bears a similarity to the properties of the devices used to fabricate a computer.

The most popular, reliable, economical, and rapid components used in computers have two stable states and are hence called bistable devices. Such devices as relays (energized—unenergized), gas tubes (conducting—nonconducting), magnetic cores (magnetized in one of two directions), and flip-flops (a pair of vacuum tubes or transistors, one and only one of which is conducting) are examples of bistable devices.

A piece of "yes-no" information is called a BInary digiT, often contracted to "bit."

The machine character code for the written character symbol is most often constructed of bits. Machine character codes which have five possible "yes-no" positions are called five-bit characters. The principles of construction and manipulation of the machine codes and languages are discussed in Chapters 7 and 8. Machine character codes for written character symbols are simply referred to as machine characters.

#### Words

Machine characters are assembled to form computer "words" which are not usually the same as written-language words. They are the unit multiples of machine characters. Some computers are restricted to handling words of a fixed size and are called fixed-word-length computers; others not having such restrictions are called variable-word-length computers.

FIXED WORD LENGTH. All transfer, processing, and editing of data or arithmetic in a fixed-word-length computer is done with groups of characters of fixed length.

VARIABLE WORD LENGTH. The groups of characters manipulated are not fixed in length. Some means of distinguishing the end of one word and the beginning of the next is required. Distinction may be made by

- 1. the position of this information with respect to the rest of the data,

- 2. a special symbol between the two words that delineates them, or

- 3. a space or blank between the words.

In such a computer a part number may be a 20-character word and the part type or classification may be a one-character word.

The variable-word-length computer does have a maximum length which no word can exceed, determined by the physical structure of the computer.

#### The Block or Blockette

It is handy to have a unit of information larger than the word. Such a unit is called a block (or sometimes a blockette). A block in a fixed-word-length computer consists of a fixed number of words. Thus a 12-word block in a computer having a word size of ten characters will consist of 120 characters. In a variable-word-length computer a block of information is again of fixed length. Since the words are not of a fixed length, the block must be designated in terms of characters. Thus, a variable-word-length computer could also have a block of length 120 characters.

#### Field

When space is not at a premium, it is desirable in a fixed-word-length computer to use one word or a multiple of words to represent each "package" of information. Sometimes space is scarce and it is required to pack the information as closely as possible. The result is that packages of information may overlap from one word to the next. Thus, a 12-character part number would require two words in a fixed-word-length machine of word size ten; therefore eight character spaces would go to waste in the second word. Often another package of information of eight characters, such as the number of the department making the part, is inserted. A package of information that is a fraction (proper or improper) of a word length is referred to as a field.

A field might be considered to be a variable-word-length word in a fixed-word-length computer.

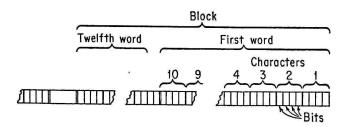

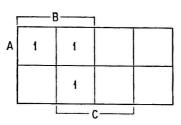

FIGURE 2.1. Data structure.

Figure 2.1 shows a 12-word block with ten-character words and fourbit characters. The first (right-hand) word contains field A of five characters. Field B spans two words.

#### 2.3. STORAGE

### Memory (Long-Term)

The memory may be used to store large quantities of information. It is handy for holding such things as reference tables; it can store vast amounts of information required during processing; it can accumulate information until enough is collected to be sent to the output equipment; it can be used as an integral part of the machine, as in bookkeeping or inventory applications.

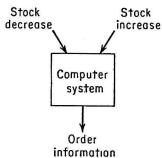

The entire inventory of a large company may be kept in a large memory. Each day the contents of this memory may be adjusted by subtracting withdrawals and adding new items received. The output required of a computer for this application consists of various records needed by management and orders for items in insufficient supply in the inventory. These records may be produced directly from memory.

Memory is rated, as are other types of storage, by the number of words or the number of characters that it will hold.

### Buffers (Intermediate)

In large computers where the processing of information constantly requires reference to the memory, it would often be inconvenient to stop processing in order to take out or put information into the memory. To prevent this kind of slowdown, an intermediate storage unit, often called a buffer, is used. Big blocks of information can be transferred quickly from the memory to the buffer or from buffer to memory without detracting from the processing in the main computer. The input or output operation can go on between the input or output equipment and the buffer without interfering with computer operation.

### Registers (Short-Term)

Information must be quickly available to the computer during processing. A word or field of information is held in a register while it is operated upon; the operation performed may be arithmetic or editing. A word or field which is operated upon, or with, is called an operand. Two numbers are added together directly from registers.

Registers operate much like a roundhouse in a railroad yard. They take the data (locomotives) out of storage (yard houses) and get them on the right track.

The length of a register is a single word for a fixed-word-length computer. In a variable-word-length computer it must hold a word of the maximum length used in the computer. The time required to place information in the register or to take it out of the register is called one word time.

#### Address

A storage medium of any consequence will be able to store a plurality of pieces of information; thus some means must be available to refer to the site of a particular datum. An address is the label for the physical location within the memory where the information is stored. Each storage position has a unique address. Directions can be given to the computer to find information or to store information by reference to the address. The address is a set of coordinates defining a memory cell. In practice it is usually a multidigit number.

#### Access

The means by which information may be entered or withdrawn from storage is referred to as access. The sequence in which this is done classifies memories into three types: (1) serial, (2) arbitrary, or random, and (3) random sequential.

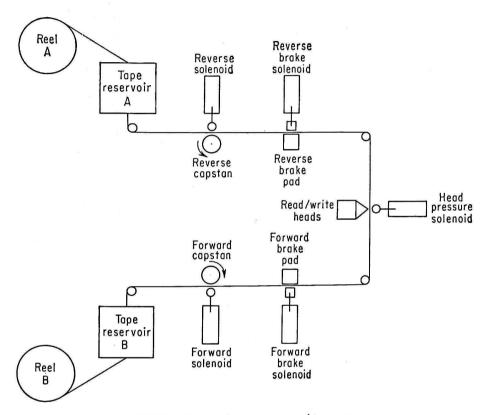

SERIAL. The information is entered into or withdrawn from memory in a prescribed sequence for a serial memory. The addresses must be examined in a fixed sequence. If a datum is stored in the middle of a serial memory, then all preceding data must be reviewed before the desired information can be extracted. Information is stored serially on magnetic tape since it is written on or read from the tape in a fixed order.

ARBITRARY. A memory which does not require a fixed sequence of reference is called arbitrary. Although "random" is the more prevalent term, "arbitrary" better conveys the idea that access is independent of the previous choice of address and does not imply that this or any other choice of address is determined by chance. Information is available in the same length of time regardless of where it is stored in the memory. Thus information stored in any array of cores is immediately available by reference to its address.

Arbitrary sequential memory requires two coordinates of reference to locate information. One coordinate of reference is found immediately, whereas the other must be searched for sequentially.

Such is the case with the magnetic drum memory, where a choice of heads and tracks is made immediately but the finding of the information on the track awaits the rotation of the drum and therefore is sequential.

#### Access Time

Access time refers to the time required to insert information into or retrieve it from the storage medium. For arbitrary storage, access time is fixed; no matter where the information is, the time required to enter or withdraw it does not vary substantially. For sequential storage the access time depends upon the relative location of the information desired. Maximum access time is the time required to retrieve information stored in the position where it is most difficult to locate. (In a tape this would be at the other end of the tape.) The average access time is the time required on the average to remove information. (In the case of the tape this would be the time required to go halfway through the tape.)

### Memorization and Remembering

There is a definite similarity between the computer's memory and our own. Memorizing material is quite different from recalling it. Think of all the trouble we went to in high school to memorize that poem. How many times we read it over, saying it out loud, even writing it down. Stop a moment and try to recall it and back it comes (maybe).

The components used for memory (long-term storage) today are almost entirely magnetic and their properties can be spoken of as a group.

Entering information into a memory location must destroy the information previously stored at that address. Two pieces of information cannot occupy the same storage location at the same time. (Some authorities believe that the human memory has so many virgin addresses that it is never necessary to use an occupied location.)

To "remember" the information is a different story. Remembering may or may not destroy the information. When the recall process annihilates the information, a computer has a destructive read-out. When remembering does not affect the memory the computer has nondestructive read-out.

#### Word Time

The word time for a register is the amount of time required to withdraw or enter one word into the register. The word time for a magnetic drum memory is similarly defined and is discussed in Chapter 13.

# 2.4. ARITHMETIC

The method by which arithmetic is performed depends on a number of things. Most important of these is the coding of information. A written number symbol is represented in the machine by a fixed binary code (such as 0100 for 4). The code that is chosen for each number will affect the manner in which arithmetic is performed. The rules of performing addition with the coded numbers depend on the coding. The coding used depends upon whether arithmetic or some other function, such as editing is the primary consideration.

Subtraction, multiplication, and division can be done using only addition and one other machine function, complementation. However, there are different ways these three processes can be composed, and the speed and functioning of the computer will depend upon the method of composition.

# Logic

The computer consists of electronic components—tubes, transistors resistors, diodes, capacitors, and so forth. These components are combined to form logical elements. These logical elements, in turn, are combined to make functional units which perform more complicated logical functions. Functional units and logical elements are then grouped together to carry out one of the computer's arithmetic or editing operations. These larger configurations that perform a single computer operation are called operational units. The computer is composed of overlapping operational units.

The way in which the logical elements and functional units are associated to do the arithmetic and processing required of the computer is termed logic. The method of associating the units together actually comprises the method of reasoning of the computer and therefore can be reasonably referred to as the logic of the computer.

The coding, the logic, and the logical building blocks comprise a team and each must be chosen to assist the other.

# Speed

Historically and currently the speed of processing and of performing arithmetic in the computer depends for the most part on the access time of storage in the computer. This includes access time to registers, buffers, and the main memory.

Arithmetic time is vitally affected by the time required to do addition. Addition time depends on the system of coding used and the logic used

for addition, which, in turn, is interrelated with the choice of components. The register word time affects the addition time because operands and intermediate results must be entered into and withdrawn from registers during addition.

The time in milliseconds or microseconds or in word times specifies the speed of addition. In most modern machines, addition is independent of the numbers being added. The time required for subtraction, multiplication, and division depends on the addition time, and on the logic used. These processes are rated in word times, addition times, absolute time, or by a formula. A formula relating the size of the digits in each operand for multiplication and division is often required to determine the time necessary for these processes. This makes more difficult the estimation of the computer time required to solve a problem. Hence, time estimates for computation must sometimes be done on an average basis.

The editing speed is also dependent upon storage speeds.

#### 2.5. TIMING

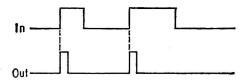

Timing here refers to the rate at which the "microscopic" processes in the computer occur. It is not the word or character but the bits used to code each character that interest us now.

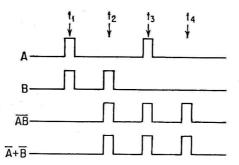

# Form of the Information

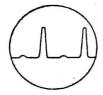

Characters coded in the form of "yes-no" information are conventionally represented electronically by a train of pulses. The presence of a pulse indicates a "yes" and the absence of a pulse indicates a "no" (or, less frequently, the reverse). The time at which the information-bearing waveform is examined to determine if a pulse is present or absent is called the bit time. If we examine the waveform over a sequence of bit times, we are able to read the character from the code represented by the pulse train.

# Rate of Handling Information

The reciprocal of the interval between the two bit times is the pulse repetition rate or the bit rate of the computer. It is also referred to as the clock rate.

The clock rate is the frequency or rate of handling pulses which are the coded representation in electronic form of the characters comprising the information to be processed. PRR is used to abbreviate the term pulse repetition rate or clock rate. Synchronism

This is a term applied to the relation to one another of the periods allotted to the operations performed by the computer. Multiplication and division may be of variable duration. If a fixed time is allotted for each such function, the computer is termed synchronous. This fixed time, of course, would have to be the largest time required for any operation to be completed. Enough time must be allotted to complete the longest operation. If the computer completes an operation before the time allotted, it waits until the period has completely expired.

This type of operation is inefficient since time is frequently wasted just waiting for the allotted operation period to elapse. Still, it simplifies the design and construction of the computer as a whole and may result in a cost saving in the initial purchase of the equipment and in increased ease of programming.

If, on the other hand, the computer starts the next operation immediately after the completion of the current operation, the computer is termed asynchronous. This type of operation increases the initial cost of the computer, but increased efficiency may result in more profitable use of the computer.

Some computers fall between these two extremes, doing some chores synchronously and others asynchronously.

# 2.6. MEANS OF INSTRUCTING THE COMPUTER

It would not be wise to design a computer which could only do one problem unless that was all that would ever be required of it (missile guidance, for example). To make a computer versatile, it is necessary to break down a problem into tasks. These tasks are unit operations which the computer performs. The original problem solution can be assembled with these tasks. Other problems can be tackled as they arise. A sequence of tasks is chosen to solve the largest universe of problems.

Tasks which are subdivisions of a problem are called instructions, commands, operations, or orders (used interchangeably in the text). The sequence in which these instructions are performed is called the routine. The person who sets up the sequence of commands is called the programmer or coder. What he does is called coding and programming. The program is the entire activity required to solve a problem on the computer; the coding reflects the sequence of operations performed by the computer. Chapters 5 and 16 are devoted to the techniques of coding and programming.

Here is a good place to pause a moment to note the prevalent ambiguous use of the term "code." We first encountered this term in connection with the language used within the computer. Here "code" conveyed the

machine representation of a human-language symbol. As now encountered, "code" means a symbolic representation, which calls for a machine order or instruction. This instruction code may take two forms: the human-language instruction code is a letter and/or number combination that conveys to the coder or programmer the instruction to be performed at a given relative time by the computer; the machine language translation of the instruction code or the "coded code" is the machine language datum that causes the computer to perform the instruction desired by the coder or programmer. To illustrate this, the instruction code for the instruction Add for the Datatron 205 is 74; the coded code or machine language instruction code for Add for the Datatron 205 is 0111 0100. More detail on this point appears in Chapter 4.

The routine composed by the coder may be stored within the memory of the computer, just as the information or data to be processed are stored. The computer can then "get its orders" by referring to its memory; it is said to be internally programmed. In all other cases the computer is said to be externally programmed.

#### 2.7. CHECKING

Information is manipulated, edited, and moved about from place to place within the computer. It is of prime importance that this information be kept correct at all times. Information may be damaged at any time during processing or transfer by the dropping of a pulse or the picking up of an extra pulse. Such damage must be detected at the earliest opportunity. A detected error should be corrected if possible, or the solution so far completed discarded as worthless. There's no sense in finishing the problem with an error present, is there?

# Checking Arithmetic

When one number is added to another the result may be checked by subtracting one of the numbers added from the sum. The result should be the other number. To check we perform the complementary arithmetic process. Here we refer to addition and subtraction as complementary; multiplication and division are also complementary. An example is shown in Figure 2.7.1.

| Problem | Check | Problem | Check      |

|---------|-------|---------|------------|

| 2319    | 10060 | 2319    | 6          |

| +7741   | -2319 | +7741   | · <u>1</u> |

| 10060   | ¥7741 | 10060   | 7          |

FIGURE 2.7.1. Checking by performing complementary arithmetic.

FIGURE 2.7.2. Casting out nines.

An old method of checking arithmetic which you might remember from elementary school is known as "casting out nines." This method may be found in an arithmetic book or a text on number theory. An example is given in Figure 2.7.2.

# Information Corruption

In transferring information, one of the bits may be corrupted and a zero misread as a one, or a one misread as a zero. The coding used may offer a means for checking the information. Checks are of two kinds.

Error-detection coding. The corruption of one bit of such a code can be detected. The machine will recognize this type of corruption by the presence of a forbidden code.

Error correction. By means of more elaborate codes, not only may the presence of an error be detected, but also the exact bit which was corrupted. The corruption can thus be completely eradicated.

# **PROBLEMS**

- 1. Draw a block diagram showing the various language translations which might take place in entering data into and retrieving data from the computer.

- 2. Show how the message below might be entered into a variable-word-length computer using asterisks as separators; into a fixed, ten-characters-per-word computer without spanning two words with one field.

- (a) Felt brake-drum cover 39R1.

- (b) Azimuth 39.17, elevation 72.38.

- 3. (a) Draw a triangle illustration of the hierarchy of the computer. Include functional units, operational units, circuit elements, logical elements.

- (b) What is computer logic?

- 4. Do and check by casting out nines and by complementary arithmetic:

- (a)  $258 \times 381$

- (b)  $109,153 \div 3851$

- (c) 3457 1085

- 5. Contrast long-term, intermediate, and short-term memories for (a) size, (b) name, (c) use, (d) access.

Contrast the ways in which access is made to each kind of memory.

### THREE

# SPECIFYING THE COMPUTER FOR THE PROBLEM

#### 3.1. INTRODUCTION

In this chapter business applications are emphasized. We discuss what happens from the time a company discovers that there are problems that might suitably be solved by a digital computer installation to the time when that installation is working satisfactorily on the problems.

There are five major phases in the procedure, each of which is discussed in a separate section of this chapter. We may list the phases as follows:

- 1. State the problem in such a way that the applicability of computer methods may be determined.

- 2. Make an initial analysis, setting forth in a general way how a computer would solve the problem, and go on to determine the computer characteristics that the problem requires.

- 3. Decide whether the computer should be bought, leased, or constructed. A consideration of the important features of design and construction enters here.

- 4. Analyze the application of the chosen computer to the problem—this is similar to the initial analysis, but is pursued to greater depth and a specific computer is kept in mind.

5. Develop operating procedures, and set the computer to work on the problem!